Cadence发布业界首款基于机器学习引擎的新版数字全流程 全面优化设计流程,改善设计质量并提高3倍吞吐量

楷登电子(美国Cadence公司)近日发布已经过数百次先进工艺节点成功流片验证的新版CadenceÒ 数字全流程,进一步优化功耗,性能和面积,广泛应用于汽车,移动,网络,高性能计算和人工智能(AI)等各个领域。流程采用了支持机器学习(ML)功能的统一布局布线和物理优化引擎等多项业界首创技术,吞吐量最高提升3倍,PPA最高提升20%,助力实现卓越设计。

经过多项关键技术,全新Cadence数字全流程实现了PPA和吞吐量的进一步提升:

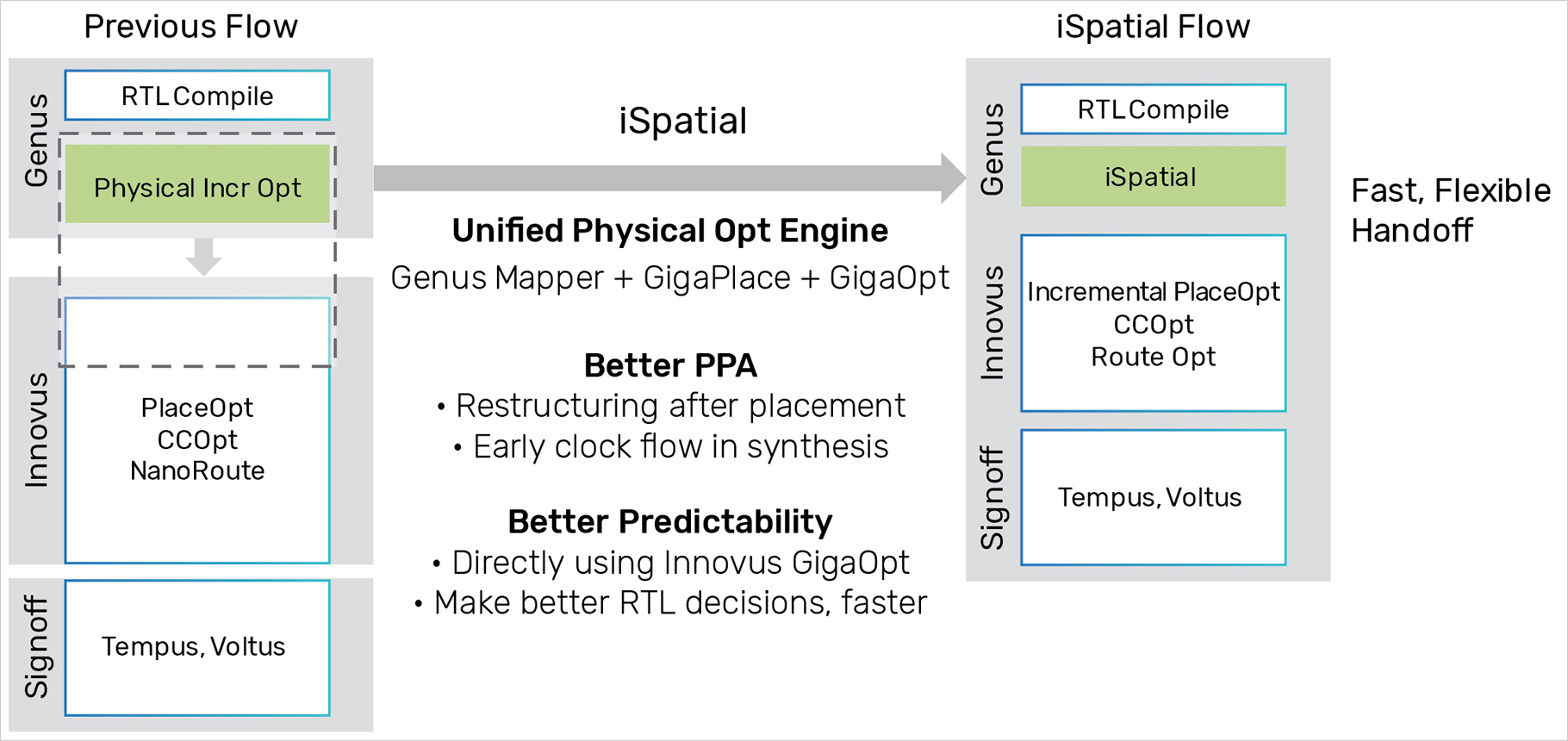

· Cadence数字全流程iSpatial技术:iSpatial技术将Innovus™ 设计实现系统的GigaPlace™ 布线引擎和GigaOpt™ 优化器集成到Genus™ 综合解决方案,支持布线层分配,有效时钟偏移和通孔支柱等特性。iSpatial技术让用户可以使用统一的用户界面和数据库完成从Genus物理综合到Innovus设计实现的无缝衔接。

· 机器学习(ML)功能:ML功能可以让用户用现有设计训练iSpatial优化技术,实现传统布局布线流程设计裕度的最小化。

· 优化签核收敛:数字全流程采用统一的设计实现,时序签核及电压降签核引擎,通过所有物理,时序和可靠性目标设计的同时收敛来增强签核性能,帮助客户降低设计裕度,减少迭代。

“基于已经广泛采纳的集成流程,全新的增强版数字全流程进一步强化了Cadence在数字与签核设计领域的领导力,助力客户实现SoC卓越设计,”Cadence公司资深副总裁兼数字与签核事业部总经理Chin-Chi Teng博士表示。“我们与客户紧密合作,缓解大规模设计下日益紧张的时间压力,提供高效达成PPA目标的全部所需。”

Cadence数字全流程包括Innovus设计实现系统,Genus综合解决方案,Tempus时序签核解决方案和Voltus IC电源完整性解决方案。流程为客户提供实现设计收敛的快速路径和更好的可预测性,支持公司的智能系统设计™ 战略,助力实现高级节点片上系统(SoC)的卓越设计。

客户反馈

“我们一直不遗余力地让高性能核心满足越来越高的性能目标。通过Innovus设计实现系统GigaOpt优化器工具新增的ML能力,我们得以快速完成CPU核心的自动训练,提高最大频率,并将时序总负余量降低80%。签核设计收敛的总周转时间可以缩短2倍。"——MediaTek公司计算和人工智能技术事业部总经理,Dr. SA Hwang

MediaTek公司计算和人工智能技术事业部总经理,Dr. SA Hwang

“Cadence数字全流程的iSpatial技术可以精确预测完整布局对PPA的优化幅度,实现RTL,设计约束和布局布线的快速迭代,总功耗减少6%,且设计周转时间加快3倍。同时,Cadence独特的ML能力让我们在Samsung Foundry的4nm EUV节点训练设计模型,实现了5%额外性能提升和5%漏电功率减少。”——Samsung Electronics代工设计平台开发执行副总裁,Jaehong Park

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码