台积电2nm制程计划将对所有客户“不打折、不议价”,价格比3nm高出约50%-66%

全球晶圆代工企业围绕2nm制程的竞争愈演愈烈,据报道,台积电已将2nm制程晶圆价格定为每片约3万美元,并对所有客户实行统一价格。据半导体行业消息人士透露,台积电宣布,计划将2nm制程的生产价格定为每片3万美元,且对所有客户实施“不打折、不议价”的策略。这比目前的3nm制程价格高出约50%-66%。

台积电2nm制程良率快速攀升

得益于存储芯片领域的技术优化,台积电2nm制程自去年7月在新竹宝山晶圆厂风险试产以来,良率从去年底的60%快速攀升至当前的90%(256Mb SRAM)。供应链传出,最近台积电位于高雄楠梓科学园区第一座晶圆厂(F22厂P1)迈入量产新里程碑,月产能在1万片左右。另外,经过近4个月的厂房赶工、建置无尘室等厂务工程后,高雄2nm第二座厂(P2)进入装机阶段,预计今年底前加入试产行列,P1、P2规划今年共可达3.5万片月产能。

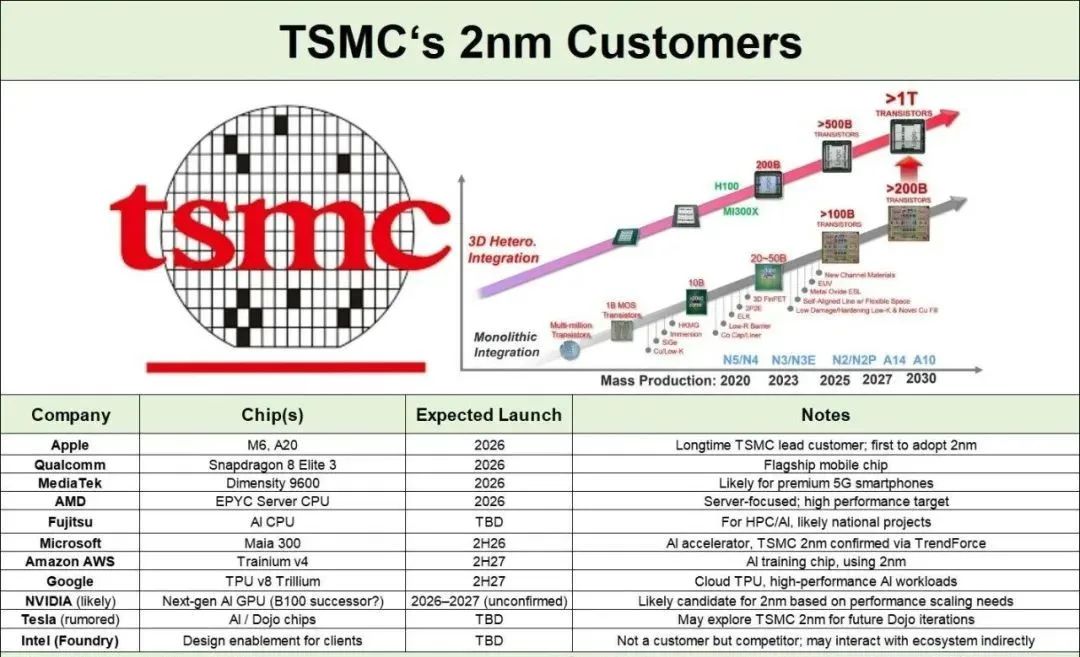

从3nm节点的初期投产经验看,良率爬坡是一大挑战。但凭借3nm节点200万片晶圆的量产经验,将2nm工艺开发周期压缩至18个月,良率仅用9个月便从30%提升至60%,预计年底将具备每月5万至8万片晶圆的投片能力。此外,台积电收到的2nm工艺流片(芯片设计验证阶段)数量是5nm工艺的四倍,显示出市场对2nm工艺的强烈需求。台积电N2的商用化将全球芯片设计企业推向新一轮“竞速赛”,AMD、英伟达、联发科、高通和苹果等关键客户均已锁定2nm产能。

4月1日起,台积电2nm晶圆的订单通道将正式开放,台积电董事长魏哲家透露,客户对于2nm技术的需求甚至超过了3nm同期。苹果有望率先锁定首批供应,根据知名苹果供应链分析师郭明錤的最新分析,2026年下半年上市的iPhone 18全系列将搭载的A20处理器或全球首发2nm工艺。

受惠AI相关客户需求热,2nm在头两年设计定案数量的高于5/3nm同期表现,并预估5年内驱动全球达2.5兆美元终端产品价值。业界传出,台积电近期向升阳半导体提出追加再生晶圆的需求,显见2nm先进制程订单增加超过预期。2025年Q1,其营收达257.8亿美元,同比增长41%,其中59%来自AI驱动的高性能计算(HPC)领域。台积电预计其AI相关营收在未来五年将保持年均增长45%,带动整体营收接近20%的年复合增长率。

台积电2nm工艺性能优秀

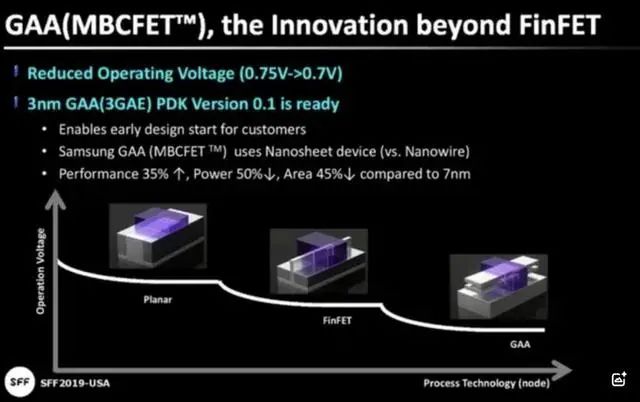

自芯片代工行业进入先进制程后,该架构也开始逐渐失效,2nm的节点就被普遍认为是“决战节点” —— 全环绕栅极(GAA)纳米片晶体管被提出。与FinFET相比,GAA架构相当于将栅极的鳍片旋转90°,然后再在垂直方向上分成了多条鳍片,来增加其与沟道的接触面积。2nm制程标志着台积电首次引入GAA晶体管架构,即纳米片(nanosheet)技术,取代此前长期主导的FinFET晶体管。

实际上,GAA技术在三星的3nm制程中就被抢先采用,但由于开发难度过大且时间紧迫,其3nm试生产的良率不足20%,根本无法满足量产需求,甚至无法自给自足。苹果、高通、联发科、英伟达等科技巨头都将3nm芯片的订单交给了台积电,台积电几乎包揽了全球的3nm芯片产能。

相比于三星的“一步到位”,台积电则选择在2nm工艺中首次引入GAA架构。此前在IEDM 2024大会上,台积电披露了N2工艺的关键技术细节和性能指标:对比3nm,晶体管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。这一提升得益于GAA技术更低的阈值电压,从而降低了漏电功耗。

对比传统的FinFET晶体管:台积电N2工艺可以在0.5-0.6V的低电压下,获得显著的能效提升,可以将频率提升大约20%,待机功耗降低大约75%;还应用了全新的MOL中段工艺、BEOL后段工艺,电阻降低20%,能效更高;针对高性能计算应用,台积电2nm还引入了超高性能的SHP-MiM电容,容量大约每平方毫米200fF,可以获得更高的运行频率。

整个N2系列将增加台积电的全新NanoFlex功能,该功能允许芯片设计人员混合和匹配来自不同库的单元,可以优化沟道宽度以提高性能和功率,然后构建短单元(以提高面积和功率效率)或高单元(以提高15%的性能)。

同时,台积电还在研发N2P(N2增强版本),计划2025年完成资格认证阶段,2026年下半年量产。与原始N2相比,N2P功耗降低5%-10%(在相同频率和晶体管数量下)或性能提高5%-10%(在相同功率和晶体管数量下),并完全兼容N2。在欧洲开放创新平台论坛上台积电宣布,Cadence和Synopsys的所有主要工具以及西门子EDA和Ansys的仿真和电迁移工具,都已为台积电的N2P制造工艺做好准备。

用不起的台积电2nm工艺

目前,台积电已在新竹宝山工厂开始了2nm工艺的试产工作(每月5000片晶圆的小规模生产),初期良率是60%,这意味着有将近40%的晶圆无法使用,每片晶圆的代工报价可能高达3万美元。

2016年,制程技术演进至10nm后,报价增幅显著,达到6000美元;进入7nm、5nm制程世代后,报价破万;相比于2nm,目前3nm晶圆的价格大约在1.85-2万美元/片之间。以iPhone 18 Pro系列首发搭载的A20 Pro处理器为例,这颗首个利用台积电2nm工艺制程的芯片,价格将由目前的50美元上涨至85美元,涨幅高达70%。由于先进制程报价居高不下,芯片厂商成本高企,势必将成本压力转嫁给下游客户或终端消费者。

2024年,高端智能手机集体用上了基于3nm工艺的旗舰芯片:骁龙8至尊版、天玑9400、A18系列都采用了台积电3nm工艺。相比4nm工艺,3nm工艺的代工费贵了不少,加上内存储存等核心元器件的涨价,让骁龙8至尊版/天玑9400旗舰机的价格普遍上涨。以小米为例,小米15的起售价,比上代就上涨了500元。

不可否认的是,高工艺的芯片确实带来了更高的性能和更低的功耗,但随之而来的高昂价格也让许多客户望而却步。而台积电之所以这么报价,当然是因为:没有对手。据报道,台积电已调整了对客户的2025年代工报价,以缓解海外设施高昂运营成本和2nm部署成本造成的毛利率损失的影响。台积电的高定价政策并非仅仅反映了生产成本,而是一种通过将有限的初始产能集中在“高端需求”上来实现利润最大化的策略。

值得注意的是,由于2nm晶圆单片成本高达3万美元,台积电希望通过进一步降低成本来吸引其他客户,因此可能在4月推出「CyberShuttle」服务来降低客户成本,即允许在同一测试晶圆上评估芯片,以减少研发开支。台积电在3nm芯片的全球竞争中几乎达到垄断地位,而最新消息来看,其在2nm技术上的优势已经远超同行 —— 三星目前为止仍未吸引到足够的客户来参与其2nm芯片的代工,英特尔则在技术上落后。

台积电N2还有对手吗?

半导体设计企业在3nm以下的先进工艺中对台积电的依赖程度不断加深,2nm芯片的价格如此高昂,一方面是因为各个环节的成本都在上升,另一方面也是因为台积电在芯片代工行业中,已经形成了事实上的垄断。而台积电产能不足、价格上涨,半导体设计企业对代工厂商多元化的意愿也在不断增强。那么在进入2nm工艺时代后,行业内还有能掣肘台积电的力量吗?

台积电的竞争对手三星正在全力提升2nm制程良率,并推动现有客户日本PFN等公司进行测试,以争夺2nm制程市场。此前业内就有传闻称,三星在3nm工艺制程上跌了个大跟头后已经有暂停3nm工艺开发,全力“All in”2nm工艺的打算,立志要在2nm工艺制程上完成追赶。

业内人士透露,三星在其平泽P2和P3生产基地的4nm、5nm和7nm制程中,已有超过30%的代工生产线停产,并计划在年底前将停产比例扩大至约50%。而3nm的情况更不乐观,报道指出三星目前第一代的3nm制程工艺目前良率只有60%。考虑到其位于华城的S3产线,在还未正式量产3nm晶圆前,就开始计划将设备升级为2nm工艺的配套设备,这种说法可能并非空穴来风。

据报道,三星2nm工艺的良率约为40%,为了恢复技术信誉并获得客户认可,该公司正采取相对低价和快速响应的策略来吸引新客户。但按照三星的规划,其2nm产能至少要到2027年才能量产。

三星2nm工艺不仅要面对良品率较低的老问题,而且还要将性能功耗提升到客户所期望的水平,这可能是承受了数万亿韩元亏损的三星代工业务的最后机会。三星代工翻车是从高通骁龙888芯片出现了过热问题开始,这是由于当时三星的5nm工艺结合Arm的X1超大核心功耗过高导致的,因此从骁龙8+ Gen1开始,高通骁龙8系平台转投台积电。如果骁龙平台转向三星2nm工艺制程,那么其功耗问题将会是业内关注的热点。

相关报道称,高通在测试三星的2nm工艺,不过尚未敲定高通是否会将订单交给三星。毕竟在骁龙8+Gen1表现不俗之后,高通的骁龙8Gen2、骁龙8Gen3、骁龙8至尊版等旗舰芯片,都是由台积电代工。而且在骁龙8至尊版转向自研CPU架构后,CPU超大核主频达到了惊人的4.32GHz,功耗要求极高,现在确实是只有台积电才能做到。

另一边的英特尔,虽然已经完成18A工艺(等效2nm)的试生产工作,但被曝良率过低,且公司正处于动荡期,量产时间也是遥遥无期。台积电过于有统治力的市场主导地位在2nm制程上仍会延续。从目前的进度来看,先进制程的主要竞争者在2nm上依旧不能望其项背。

台积电在美2nm生产线最早可能在2026年投产

台积电宣布将最先进的2nm制程技术加速转移至美国亚利桑那州生产基地,这仅比在中国台湾本土的生产线投产晚一年,此前“海外工厂技术至少落后一代”的承诺彻底失效,标志着其全球布局逻辑发生根本性颠覆。这一决策标志着半导体产业格局的剧变,更是美国重构半导体产业链的野心与全球化退潮的残酷现实。

台积电目前正在亚利桑那州的Fab P3工厂筹备2nm(N2)生产线,最早可能在2026年投产。根据规划,美国工厂将承载台积电30%的2nm产能,结合3nm/4nm等其他制程,美国基地总产能占比将突破40%。未来甚至或许有更激进的规划,后续第四座晶圆厂可能直接导入1.4nm(A14)工艺,真正与美国实现“技术零时差”的。官网信息显示,与台积电领先业界的N2制程相比,A14将在相同功耗下,提升达15%的速度;或在相同速度下,降低达30%的功率,同时逻辑密度增加超过20%。

台积电77%的营收来自北美客户(苹果、英伟达、AMD等),而这些科技巨头在《芯片法案》压力下要求「在地化生产」以保障“供应链安全”,所以对这家中国台湾巨头来说,在美国建立强大的芯片网络至关重要。目前,台积电在美国的投资已追加至1650亿美元,远超初期计划,其亚利桑那州基地将建设6座晶圆厂、2座先进封装厂和1座研发中心,首次在北美构建从晶圆到成品的完整生态系统闭环。台积电正打破「制造-封装分离」的传统模式,配套建设的先进封装厂将引入SoIC及CoPos等3D集成技术,终结当前“美国造晶圆、台湾做封装”的割裂流程。

同时,特朗普政府正在通过监管措施为这家芯片巨头提供支持。美国财政部长斯科·贝森特(Scott Bessent)透露,台积电亚利桑那州工厂目前仅能满足美国芯片需求的7%,而其发展受限的一个重要原因是过度监管导致项目延误,频繁的监管干预给台积电的项目推进带来了巨大挑战。特朗普政府正专注于解决监管问题,通过简化流程帮助台积电在美国建立更高效的供应链。然而,鉴于美国芯片需求的规模,台积电可能需要数年时间才能建立一个完整的供应链。

在这场深刻转变中,中国台湾地区自身正陷入前所未有的结构性困境。尽管本土技术领先地位短期内仍能保留,如70%的2nm核心产能,但随着产业链条因全球区域化而被强制拉伸:已有超过50家关键台湾设备与材料供应商随台积电大举赴美投资,长期发展面临着核心研发资源被稀释、高端订单被持续分流以及完整产业链优势逐步瓦解的风险。

台积电的决定绝非孤例,而是整个半导体产业在全球政治经济格局剧变下深刻裂变的集中体现。未来五年,纳米时代的权力分配将取决于两大核心:量产能力与地缘适配性,而地缘风险正重塑游戏规则。美国对EUV光刻机的出口管制、日本在半导体材料领域的垄断(全球52%份额),以及欧盟对成熟制程的本土化扶持,都在加速全球供应链从“全球化分工”转向“区域化堡垒”。对于大陆产业而言,突破先进制程瓶颈、实现国产化设备替代与完善本土产业链生态系统(如EDA工具、材料、以及核心IDM厂商的协同)则是长期而艰巨的任务。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码