OTN帧头定位电路优化研究

编者按:在OTN帧结构中,Serdes在从高速的串行数据中恢复出数据后,数据只是按顺序以64bit为宽度重新放置,并没有按字节对齐,所以后续电路无法直接使用这样的数据。需要帧头定位电路找到帧头后,把所有的数据按字节对齐。但是将OTN数据转换为并行的数据后,存在着数据速率高,位宽大的问题。在ASIC或FPGA中,大量的大位宽的数据,是不容易运行在较高的速率下的。所以需要对帧定位电路进行简化,以使得电路在大位宽时,仍然能够进行高速运行。研究了OTN数据的帧结构后,提出了一种适合于高速率的、大位宽的处理电路。

引言

在ITU-T G.709协议中,ITU-T规定了OTN的网络帧结构。OTN使用了和SDH类似的帧结构,帧定位信号(Frame Alignment Signal)也是相同的。但是由于OTN的信号速率非常高,如OTU2的速率达到10Gbps以上,OTU3速率达到43Gbps以上,不能直接使用SDH的帧定位电路。以OTU2为例,在Serdes将串行信号变为并行信号后,如果还按照8bit的数据宽度,则信号速率需要达到1.25Gbps左右,这无论对于FPGA处理还是ASIC,速率都是过高而不能处理的,所以需要将数据宽度进一步加大,以降低信号速率。在本项目中,使用了64位的数据宽度,这时的信号速率为167Mbps。对于这样高速而且宽位数的数据处理,如果还按照传统的帧头定位电路来处理,电路的速度上不去,会导致电路处理不能达到要求,所以需要简化帧头定位电路,以达到高速率、高位宽的信号处理要求。

传统的帧定位处理方法

OTN帧结构

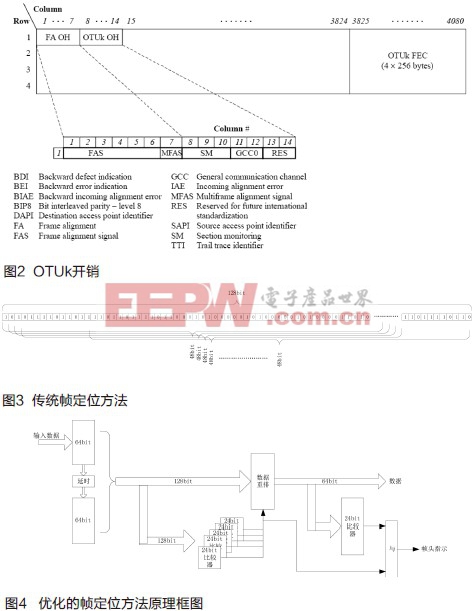

在ITU-T的G.709协议中,ITU-T规定了OTN的帧结构,如图1所示。

OTUk帧结构是4行,4080列的结构。在每一帧的开始处,首先是帧定位信号(FAS),然后是复帧定位信号(MFAS)和其它开销字节。详细如图2所示。

在OTUk帧数据中,FAS信号是不经过扰码的,除FAS信号外的信号,都是经过扰码的。所以只要在整个数据中,只要找到了FAS(即0xF6F6F6282828)信号,就将整个帧头找到了,整个帧的结构就随之确定了。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码