基于双核Nios II系统的数字预失真器设计

在现代无线通信系统中,功率放大器(PA)是整个发射机中最为关键的部件之一。然而,PA固有的非线性特性会对通信质量造成严重影响。数字预失真技术作为一种高效的功放线性化方法,近年来得到了广泛重视和研究[1-4].传统的数字预失真器一般采用FPGA+DSP的方案,结构较为复杂,成本较高。本文在FPGA芯片中构建了SoPC系统,设计了一个自适应数字预失真器(DPD),它具有集成度高、成本低等优点。同时,采用并行RLS算法提取DPD模型参数,降低了传统RLS预失真算法的复杂度。采用双核Nios II并行操作,提升了硬件处理速度,保证了预失真处理的实时性和敏捷性。

1 DPD多查找结构

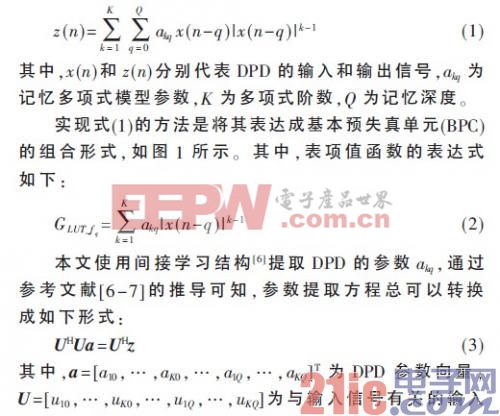

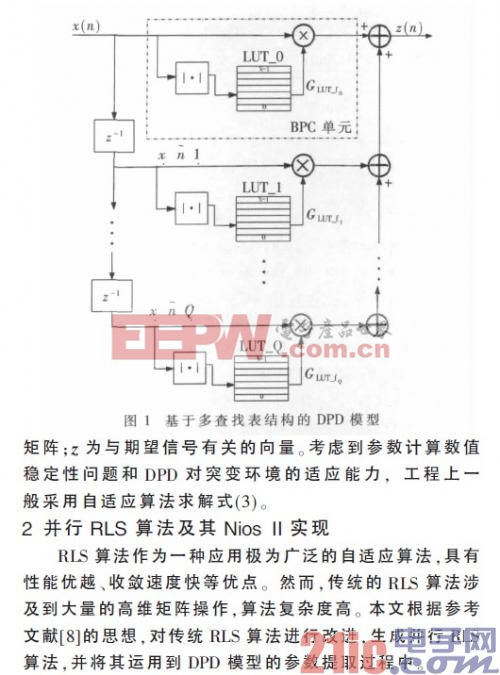

本文采用记忆多项式模型[5]作为DPD的行为模型,表示为:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码