基于SOPC的异步串行通信IP核设计

随着嵌入式技术的发展,基于SoPC技术的嵌入式系统所具有的软硬件可裁减、可扩充、可升级以及可在线修改的特点越来越受到人们的重视。SoPC系统通常具有以下基本特征:采用大容量可编程逻辑器件来实现,单芯片、低功耗;至少包含1个以上的嵌入式处理器IP核;具有一个或多条片上总线作为系统扩展功能的接口;具有充足的片上可编程逻辑资源,用户可以根据需要扩充功能部件。

异步串行通信协议(UART)以低成本、高可靠性等优点而广泛应用于嵌入式系统中,多篇文献也讨论了UART协议的硬件设计方法,但多数只限于讨论UART协议的硬件实现,缺少从SoPC系统的角度论述UART IP核的设计方法。本文以UART IP核和PLB总线为例,讨论了在SoPC系统下UART IP核的设计方法,该方法对其他IP核的设计有一定的参考作用。

1 UART协议介绍

UART是一种串行异步通信方式,它采用RS232电平在串行链路上进行全双工的通信,其数据传输格式如图1所示:UART协议在空闲时为高电平,通过发送起始位提示接收方数据传输即将开始,接着传输8位有效数据位和奇偶检验位,最后发送停止位表示一个字符传输完成。

2 SOPC UART通信系统介绍

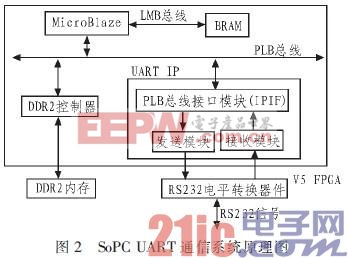

本文设计的SOPC UART通信系统主要包括MicroBlaze处理器、PLB总线、UART IP核和DDR2控制器IP核,如图2所示。

MicroBlaze处理器是Xilinx公司针对其FPGA器件优化的32位微处理器核,它采用RISC(Reduced Instruction System Computer)架构和哈佛总线结构,具有独立32位数据和指令总线,能够高速执行和访问片上存储器和片外存储器上的程序与数据;提供本地块存储器总线(LMB)、处理器本地总线(PLB)等总线接口。

PLB总线作为IBM CoreConnect总线协议簇中的一部分,广泛的应用于IBM PowerPC处理器架构中。该总线具有总线地址空间大,总线吞吐率高,能支持多个主从设备连接等特点。如图3所示,MicroBlaze处理器通过PLB总线与UARTIP核、DDR2控制器相互连接,各部件之间通过PLB总线协议进行交互。其中,MicroBlaze处理器作为主设备完成系统控制和UART通信流程控制,UART IP核作为从设备在主设备的控制下完成异步串行通信,DDR2存储指令和数据。

MicroBlaze处理器和DDR2控制器采用Xilinx公司提供的IP核,UART IP核由用户编写逻辑,它是文中设计的主要内容,对此模块的设计将在下一节进行详细阐述。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码