基于DSP开发系统设计与实现

3 时钟电路设计

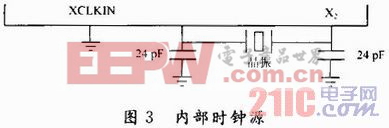

TI的DSP时钟电路分为三类:晶体电路、晶振电路和可编程时钟电路。其中时钟电路如图3所示。

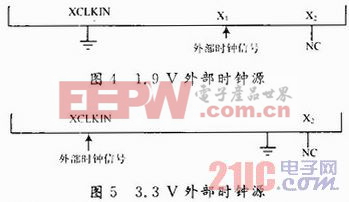

其特点是:结构简单,但频率范围较小,一般为20 kHz~60 MHz,驱动能力较弱。晶振电路利用外部独立的时钟源给系统提供时钟。其特点是:频率范围较大,一般为1 Hz~400MHz,驱动能力强,可为具有相同时钟的多DSP系统使用。可编程时钟电路可以为外设提供不同的时钟,适用于不同时钟源的系统使用,频带宽度可达 200 MHz。F28335的外部时钟可以有两种输入方法,如图4~图5所示。

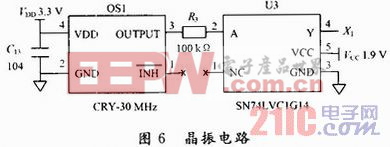

该设计使用1.9 V的外部时钟源晶振电路,如图6所示。其中,100Ω电阻用来衰减外部杂波的干扰,提高时钟波形的质量,SN74LVC1G14是单路施密特反向触发器。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码