π/4-DQPSK差分解调器的数字化FPGA设计与实现

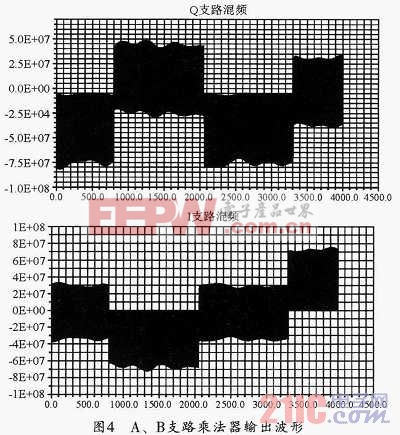

下面是A、B两路乘法器的LPF输出:

![]()

3 结束语

π/4-DQPSK差分解调算法的所有部分均可由VHDL编程实现。目前,整个过程已经经过功能仿真和时序仿真,并用OUARTUS II进行了综

合、映射、布局布线,现已成功下载到Cyclone II中运行。可满足预期的设计目标。该方案实现简单,速度快,占用硬件资源少,非常适合工程应用。其软件和硬件相结合的方法还具有体积小、功耗低、集成度高、可软件升级、抗干扰能力强等特点,符合未来通信技术发展的方向。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码