π/4-DQPSK差分解调器的数字化FPGA设计与实现

经过混频后进入解调器的信号φ(t)的波形如图3所示,设上支路为A,下支路为B。那么,经延迟移相后,其上、下两支路分别为:

而乘法器的输出为:

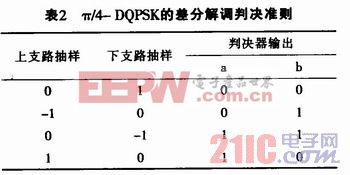

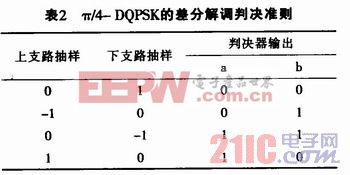

其A、B支路的乘法器输出波形如图4所示。表2所列为π/4-DQPSK的差分解调判决准则。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

经过混频后进入解调器的信号φ(t)的波形如图3所示,设上支路为A,下支路为B。那么,经延迟移相后,其上、下两支路分别为:

而乘法器的输出为:

其A、B支路的乘法器输出波形如图4所示。表2所列为π/4-DQPSK的差分解调判决准则。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码