PCM串行数据流同步时钟提取设计

2 同步时钟提取过程编程实现及仿真结果

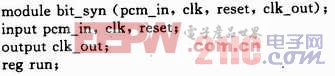

同步时钟提取模块的声明代码如下:

输入端口为pcm_in,clk和reset,分别为PCM输入信号,全局时钟输入和复位信号,输出端口仅一个,clk_out采样时钟。

模块中两个计数器count1和count2,分别为前述分频计数器和计时计数器。

三个标志位:run,changed和overflow,后两个在第二部分中详细介绍过功能,run标志位为模块工作状态标志位,run位置1模块运行;changed标记本码元采样状态,已经采样过则该位置1;overflow标记计时计数器溢出状态,已溢出则该位置1。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码