数字频率信号校正的FPGA实现

3 实现方案与仿真结果

3.1 实现方案

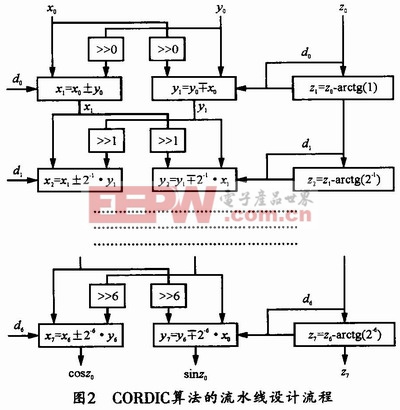

CORDIC算法的流水线流程图如图2所示,该方法采用7级流水线,故可大大提高计算速度。

3.2 仿真结果

基于CORDIC算法的正余弦信号发生器的仿真结果如图3所示,由图3可见,该算法可以实现标准的正弦波和余弦波,并可直接作为频偏校正单元。

4 结束语

本文通过对CORDIC算法的工作原理进行分析,给出了基于CORDIC算法和FPGA实现数字频率校正的实现方案。仿真结果证明,该方法可以实现标准的正弦波和余弦波信号,可以直接作为频偏校正单元来对数字频率信号进行校正。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码