基于NioslI的SOPC系统的LCD显示驱动IP核设计

3.1 任务逻辑

任务逻辑是整个驱动的核心部分。要实现对LCD的显示控制,就要按照CBG128064驱动控制器的规范及时序要求进行设计。在时序逻辑电路中,数据信号和控制信号的配合比较复杂,但又十分重要,使用有限状态机可以较为容易地设计出复杂的数字电路系统。

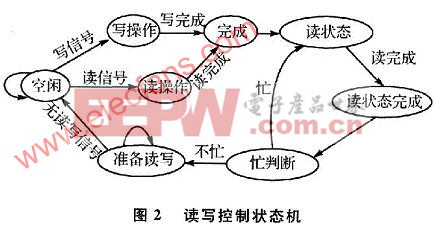

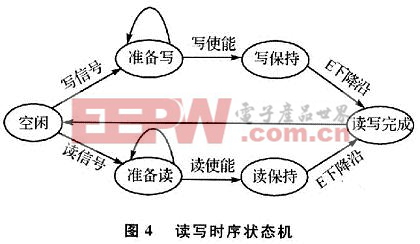

本文采用有限状态机实现显示驱动的核心逻辑。根据驱动控制器的读写命令及读写时序要求,本文设计了3个状态机,分别为读写控制状态机、读写状态机和读写时序状态机。

如图2所示,读写控制状态机用于当发生读写请求时进行忙状态检测及读写操作控制,并在每个状态给出时序状态机读写信号。

如图3所示,读写状态机给出读或者写信号,并在读写控制状态机的控制下,完成写命令、写数据和读数据之间的状态转移。在每一个状态下给出LCD显示数据及控制信号,如片选、所写数据/指令等。

如图4所示,读写时序状态机用于控制读或者写外设的时刻,当读写完成时给出读写完成信号。其中,读写信号由图2中的读写操作给出。根据CBGl28064读写时序要求,当R/W为高电平时,读取显示RAM中的数据;当R/W为低电平且在E的下降沿时,向显示RAM中写入数据。读写时序状态机的读写信号由读写控制状态机给定,其中,E为模块使能信号。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码