基于VHDL语言的99小时定时器设计及实现

3.2 显示模块

通过XUAN模块可完成BCD码的转化,再经DISP模块译码.然后输出给七段数码管。

(1)XUAN模块

XUAN可产生四位BCD码输入,并从sel端输出。该模块的管脚图如图5所示。其源程序代码如下:

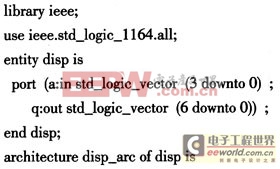

(2)DISP模块

DISP模块主要用于译码,可定义七段数码管显示的数字。其源程序如下:

关键词: FPGA VHDL 定时器 EP1C6Q240C8

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码