基于VHDL语言的99小时定时器设计及实现

3 主要模块软件程序

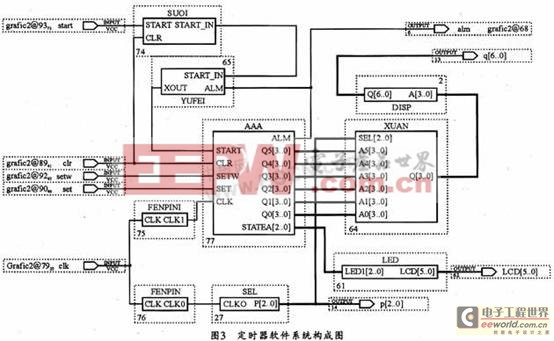

图3所示是该定时器的软件系统构成。本软件包括控制/定时模块和显示模块两大部分。

3.1 控制/定时模块

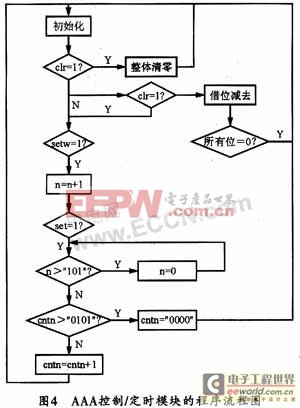

AAA控制/定时模块是该定时器的核心部分,该模块的程序流程图如图4所示。

当START为高电平时,该定时器将进入倒计时阶段。当CLK脉冲上升沿到来时,计数以秒的速度减1,直到计时结束,使ALM位为高电平为止。CLR为复位端,可用来清零,通常采用异步复位方式。SETW用于选位,高电平有效。SET用于对选定的位进行置数,也是高电平有效。ALM输出端将在定时结束时产生高电平。Q0~Q5为四位BCD码输出端口,主要用于显示。

关键词: FPGA VHDL 定时器 EP1C6Q240C8

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码