多路同步串口的FPGA传输实现

引言

随着集成电路技术的发展,FPGA和DSP以及ARM以其体积小、速度快、功耗低、设计灵活、利于系统集成、扩展升级等优点,被广泛地应用于高速数字信号传输及数据处理,以DSP+FPGA+ARM的架构组成满足实时性要求的高速数字处理系统已成为一种趋势,本文主要研究FPGA在高速多路数据传输中的应用。

系统结构

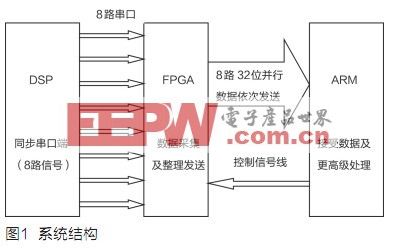

在DSP多路串行数据同时向ARM发送的系统中,因为数据通道有并行要求,应用FPGA硬件并行的特点,由FPGA并行接收多路数据,经过缓冲后再发送至ARM进行数据的高级处理的方案,系统结构图如图1所示。

如图1所示,DSP传输8路串行数据,每路数据速度为60kB/s,时钟频率为60MHz。即每秒60×32=1920kbps,由此可得FPGA向ARM发送数据带宽为60×8×32=15.360Mbit/s。根据系统的这一要求,FPGA选用Altera 公司Cyclone2 ep2c5q208c8,此型号的FPGA拥有4608个逻辑单元,142个用户引脚, 119808bit的内嵌RAM,以及2个内嵌PLL锁相环,资源丰富。

FPGA处理模块实现

DSP的串口传输方式为同步串口,每组DSP串口有4个端口,分别为:clk,frame, data_a,data_b。数据端口有两个,本例中只使能data_a,以下统一称为data。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码