Arteris栾淏:可配置高性能互连架构加速基于RISC-V的AI/ML与ADAS SoC

7月18日,第五届RISC-V中国峰会在上海进入分论坛环节。作为未来电子产业最庞大的应用范畴之一,人工智能是不可回避的话题。人工智能的飞速发展,正以年均超过100%的算力需求增长驱动底层架构的革新,“开放、灵活、可定制”的RISC-V已成为构建自主AI算力基石的战略支点。人工智能分论坛邀请各方企业探讨RISC-V架构如何利用其开源、开放、可扩展的特性,实现AI计算架构的革新,以及RISC-V架构在AI软硬件的最新进展和应用落地情况。

Arteris首席架构师栾淏详细介绍了该公司在可配置高性能互连架构加速基于RISC-V的AI/ML与ADAS SoC方面的进展情况。栾淏认为,架构和解决方案可以加速基于RISC-V的AI和ADAS应用,不过这增加了常规SoC的复杂性和尺寸,带来了下一个层次的挑战。对于互联网栾淏列举了一些挑战,比如:我们需要真正拓宽总线以进行通信、计算和内存。你看到建筑物的电线,我们看到越来越多的异构和同构关联,在这些关联中你必须支持规则和不规则的拓扑结构。基于一个典型的SoC平面图可以看到,在常规SoC上,你可以看到、2030年我们至少会有5次技术革新,包括寄存器,硅面积的15%到30%。为了解决这些关键问题,帮助集成复杂的IPS,Arteris可以在您进行区域优化的同时进行能优化和性能扩展。

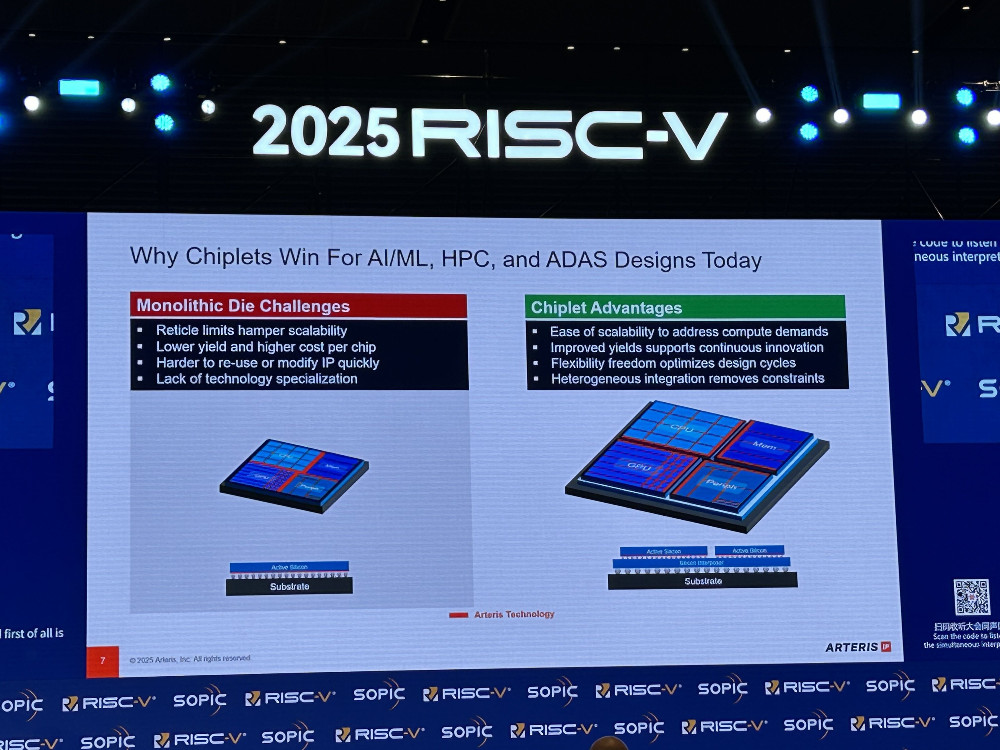

SoC面临着传输大量数据的需求,设计者也需要这样做。最大限度地提高吞吐量,同时我们需要通过关闭将计算带入内存来减少移动数据所花费的能量。当然,与此同时还需要处理所有RISC-V进程的同构问题,或者可以是与ARM和其他硬件加速器的混合使用。最后但并非最不重要的一点是我们确实看到该行业开始向多芯片和小芯片发展,RISC-V的部署,从开始以互连为例,从ACE作为总线协议开始。这里Arteris为异构集成提供的非常独特的东西,大多数是硬件加速器集成,这样我们就可以将数据从加速器带到相干域。

为了集成不同的计算元素需求,通过利用小芯片可以提高产量,大大降低了整体成本。栾淏认为最重要的部分是真的允许用户轻松地灵活控制开发周期,以及便捷地从不同的供应商那里挑选不同的IP,并专注于自己的领域,以实现自己产品的差异化。当然,异质性确实意味着其他方面的挑战。另一个方面是整合来自不同技术节点的不同模型,这也大大缩短了你上市的时间窗口,降低整体开发成本。另一个好消息是今年下半年Arteris将发布我们的多连贯的解决方案,当然在前进的过程中Arteris希望适应行业标准、并实现开放、可互操作的机会。

谈到ADAS和汽车领域,栾淏强调ADAS和汽车市场非常关注实时性,除此之外,安全也是非常关键的要素。Arteris有很多工具和机制可供选择,真正帮助客户从ASLA到SLD都能支持和获得认证。栾淏认为在集成和自动化平台,IPS真正实现了从IP库到物理设计和SoC的平滑流程,因为真正的权威不是单一的EDA公司或系统IP提供商,而是要将小型生态系统整合在一起,整合各方资源打造最适合用户需求的方案。

关键词: RISC-V 中国峰会 Arteris AI/ML ADAS SoC

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码