背面供电选项:下一代逻辑的游戏规则改变者

背面电力传输打破了在硅晶圆正面处理信号和电力传输网络的长期传统。通过背面供电,整个配电网络被移至晶圆的背面。硅通孔 (TSV) 将电源直接从背面传送到正面,而无需电子穿过芯片正面日益复杂的后道工序 (BEOL) 堆栈。

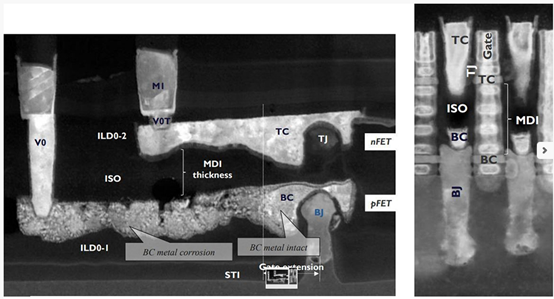

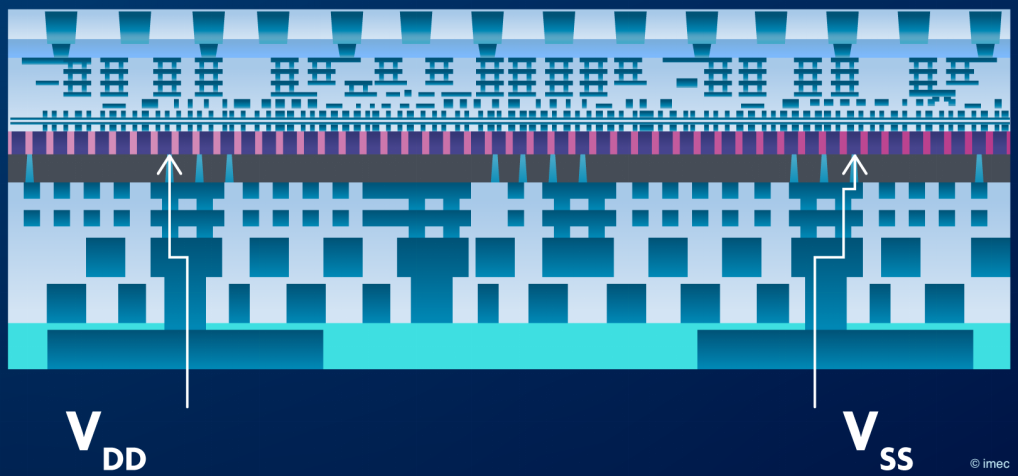

图 1 背面电力传输网络的示意图,允许将电力传输与信号网络解耦。

背面供电网络 (BSPDN) 的目标是缓解逻辑芯片正面后端线路 ( BEOL ) 的拥塞。此外,在标准单元层面,它承诺通过设计技术协同优化(DTCO)更有效地安排互连。这将有助于进一步缩小逻辑标准单元的尺寸。系统级也有望受益,系统级日益受到功率密度上升和电源电压(或 IR)急剧下降的影响。由于背面供电互连可以做得更大且电阻更小,因此 BSPDN 被认为可以显著地减少片上 IR 压降。这将有助于设计人员保持稳压器和晶体管之间允许的 10% 功率损耗裕度。它还有望实现 3D 片上系统,例如通过晶圆对晶圆键合获得的逻辑存储器。

2019 年,imec 率先提出了背面供电的概念,并与 Arm 合作量化了系统层面的优势。与此同时,BSPDN 已作为 2nm 及以上技术节点的上下文感知互连解决方案进入 imec 的路线图。最近,一些主要芯片制造商宣布在其下一代逻辑技术的商业制造工艺中引入背面配电。

特定的 BSPDN 实现:nTSV 落在埋地电源轨上

BSPDN 给芯片处理带来了新的工艺步骤和集成挑战,包括例如基板极度减薄、微米或纳米 TSV 处理、背面到正面对准以及背面处理对有源前端生产线器件的影响。E. Beyne 等人在 2023 年 VLSI 邀请论文中回顾了这些集成流程及其挑战。

通过实施这些工艺步骤,imec 实验性地演示了 BSPDN 的一种具体实施方式:背面电力传输与埋入式电源轨 (BPR) 相结合,如 VLSI 2022 所示。BPR 是一种嵌入芯片前端的垂直金属化,与标准单元平行。Imec 使用这些 BPR 将按比例缩放的 FinFET 器件连接到背面和正面。电力从背面通过 320nm 深的 nTSV 以 200nm 的紧密间距落在 BPR 上,而不占用标准单元的任何面积。背面处理不会对 FinFET 器件的前端性能产生负面影响。

图 2 显示连接到晶圆背面和正面的按比例缩小的 FinFET 的 TEM 图像 (VLSI 2022)。

块级评估:高密度与高性能案例

虽然上述工作着眼于标准单元级别的 BSPDN 和晶体管的连接性,但 imec 和 Arm 已经采取了下一步:缩小到块级别(代表集成电路的较大部分),其中的好处 BSPDN 可以得到充分收获。他们调查了与前端 PDN 实施相比,BSPDN + BPR 实施是否可以在块级别提高电源完整性。

通过设计技术协同优化 (DTCO) 进行的块级评估使我们能够评估片上 IR 压降,这是量化功率传输性能的主要指标。它还通过量化 PDN 对功耗、性能和面积 (PPA) 的影响,提供有关 PDN 对集成电路的侵入程度的信息。该研究还揭示了如何调整某些旋钮以针对特定操作条件优化 PDN。

事实证明,在高密度逻辑操作条件下,基于 BSPDN 的设计的性能优于前端 PDN 设计。在高密度逻辑中,设计经过优化,可最大限度地节省功耗并减少面积。对于基于纳米片的器件架构,这可以通过保持纳米片的宽度尽可能小来实现。但迄今为止,高性能逻辑的收益从未被量化。高性能逻辑的目标是快速开关和高驱动电流,实现通常具有更大片宽度和阈值电压的纳米片器件。功率密度要求甚至比高密度逻辑更为严格,因此,BSPDN 的优势预计将更具影响力。

BSPDN + BPR:用于高性能逻辑的块级 PPA 增强器

在 VLSI 2023 上发表的一篇论文中,imec 和 Arm 评估了 (BS)PDN 对 Arm 商用高性能 64 位处理器模块的影响 。评估了三种不同的 PDN 实现:传统的前端实现、具有前端连接的埋地电源轨,以及带有 nTSV 落在埋地电源轨上的背面电力传输网络。开发了高性能的 imec A14 纳米片工艺设计套件(PDK),以保证高性能计算模块的实际实现。内部开发的分析模型与物理设计框架结合使用,以实现块级 PPA 评估和 IR 压降验证。

与前端 PDN 相比,BSPDN 同时实现了 6% 的频率和 16% 的面积改进,并且在能耗方面没有任何缺点。与实施具有前端连接的 BPR 相比,BSPDN 的频率提高了 2%,面积缩小了 8%,能耗降低了 2%。

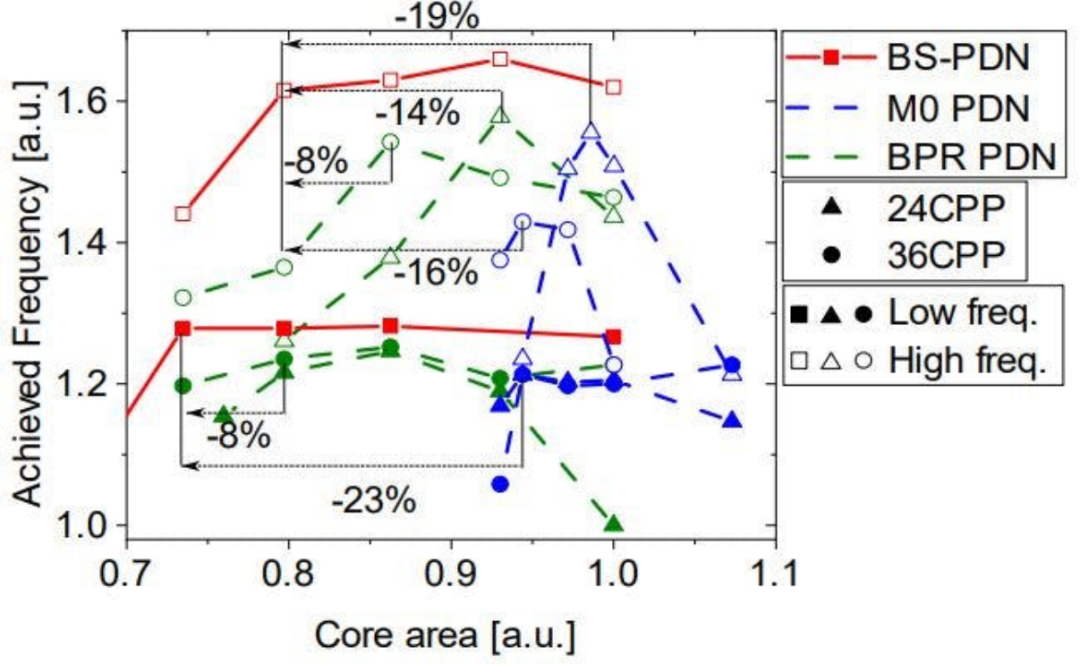

图 3 BSPDN (BS-PDN) 与两种前端实现(M0 PDN;BPR PDN)之间的核心面积比较,适用于宽松节距 (36CPP) 和紧节距 (24CPP) 以及低和高目标频率。BSPDN 在表现出性能下降之前到达较小的核心区域(如 VLSI 2023 中所示)。

研究人员为 IR 压降评估确定了 35mV 的最大允许功率损耗,相当于标称电源电压 (VDD + VSS) 的 10%。对于 BSPDN 实施,该目标是通过宽松的 nTSV 节距(4-6μm)实现的,代表「分接」功率的节距。然而,对于这两种前端选项,这一目标只能通过非常紧密的 PDN 间距(或小 CPP)来实现,从而对处理器的性能产生负面影响。

imec 团队还研究了如何进一步提高 BSPDN 外壳的电源完整性,例如通过更改 nTSV 所用的材料。当使用 Ru 代替 W 时,由于 nTSV 电阻得到改善,IR 压降可进一步降低 23%。

简而言之,BSPDN 作为块级 PPA 增强器和 IR 压降减小器的潜力可以在高性能计算环境中得到充分发挥。

扩展标准单元级别背面连接的选项

到目前为止,我们只讨论了 BSPDN 的一种实现,其中通过位于 BPR 上的 nTSV 将电源从背面传送到正面。从 BPR 开始,一个小过孔连接到中线 (M0A) 金属化的底部,以访问标准单元级的晶体管。

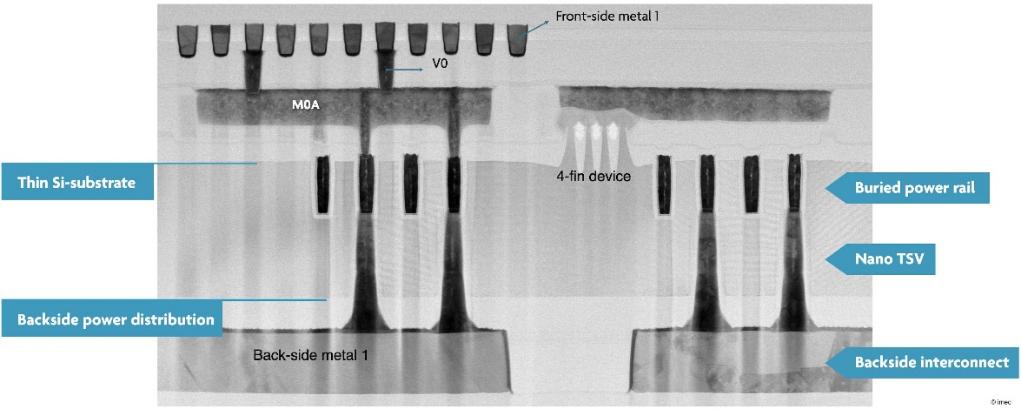

除了这种「BPR」方法之外,研究人员还在探索在标准单元级别实现背面电源连接的其他选项。在 VLSI 2023 上,imec 讨论了另外两种用于访问纳米片晶体管的连接方案。在 TSV 中间方法 (TSVM) 中,中间的高通孔将背面 metal-1 连接到 M0A 金属的侧面,而无需埋入电源轨。在第三个也是更高级的选项中,通孔将纳米片的源极-漏极外延的底部直接连接到背面金属。这种直接背面连接选项 (BSC) 分为三种类型存在差异,主要是接触面积的大小不同。在 BSC-E (epi BSC) 中,过孔仅连接到源漏外延的底部,而在 BSC-M 中,过孔还连接到金属接触。第三种 BSC-M* 通过减少浇口切割并进一步增加纳米片的「有效」宽度 (W NS ) 来扩展 BSC-M。

图 4 各种连接选项的模拟结构:TSVM、BPR 和三种类型的 BSC(如 VLSI 2023 上介绍的)。[蓝色=电源和参考电压 (V DD + V SS );浅蓝色=中间层 M0;深蓝色=BEOL 金属-1;黑色=通孔;红色=门;浅绿色=活性纳米片和电介质隔离;深绿色=金属接触 (CT)]。

各种连接方案具有不同的属性(例如 WNS),对标准单元的电气性能和扩展潜力具有不同的影响。一般来说,当从 TSVM 转向 BPR 和 BSC 时,方案变得越来越紧凑,集成起来也更具挑战性。然而,我们可以预期,随着逻辑路线图的进一步扩展,更大的集成复杂性将被更大的 PPA 增益所抵消。

实现直接背面连接

在 VLSI 2023 上,imec 量化了高密度(2nm、6T;A14、5T)和高性能(2nm 7T;A14 6T)逻辑的 2nm 和 A14 纳米片技术中不同背面电源选项的 PPA 和扩展潜力条件。性能评估的主要指标是环形振荡器的模拟频率,表示为有效驱动电流与有效电容之比 (Ieff /C eff )。

对于 2nm 节点的高性能逻辑,对于最大的 7T 标准单元,不同连接选项之间的频率几乎没有任何差异。然而,当扩展到 A14 时,TSVM 方法仍然适用于 6T 设计,但运行速度比 BPR 等慢 8.5%。总体而言,BSC-M* 明显优于其他选项(例如,比 BPR 快 5%)。

对于 2nm 节点的高密度逻辑,其轨道高度 (6T) 比高性能逻辑更小,不同选项的频率之间的差异变得更加明显。当扩展到 A14 和 5T 时,TSVM 不再是可行的选择,只考虑 BPR 和 BSC。BPR 和 BSC-M* 之间片材宽度的相对差异现在比 2nm 更大,这使得 BSC-M* 成为明显的赢家(比 BPR 快 8.9%)。

图 5 高性能逻辑(N2、7T;A14、6T)和高密度逻辑(N2、6T;A14、5T)系列的各种连接选项的模拟环形振荡器频率(如 VLSI 2023 上所示)。

综上所述,虽然 TSVM 占用更多空间,但对于较大单元(例如 2nm 7T 逻辑)来说,它仍然是一个不错的选择。然而,BPR 和 BSC 在尺寸和电气方面具有更好的扩展潜力。由于纳米片宽度和接触面积比其他选项更大,直接背面接触 BSC-M* 型显然是小轨道高度的赢家。然而,对于 BSC-M*,应权衡性能提升与更大的集成挑战。

imec 团队目前正在致力于不同背面连接选项的技术演示,并与 Arm 合作进行块级 PPA 评估。

超越背面供电

虽然硅晶圆的背面长期未使用,但利用背面的第一个实例将是用于电力传输。与此同时,imec 及其行业合作伙伴也在探索哪些其他功能也可以迁移到背面。例如,考虑全局互连和时钟信号分配。虽然电力传输是一种非常特殊的互连类型,针对最小电阻进行了优化,但分配其他类型的信号可能具有不同的属性,从而改变了背面的寻址方式。Imec 目前正在研究这种功能性背面(或背面 2.0)可能带来哪些挑战和机遇。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码