SiC器件和封装技术现状

众所周知,封装技术是让宽带隙 (WBG) 器件发挥潜力的关键所在。碳化硅器件制造商一直在快速改善器件技术的性能表征,如单位面积的导通电阻 (RdsA),同时同步降低电容以实现快速开关。新的分立封装即将推出,它能让用户更好地利用宽带隙快速开关性能。可用的标准模块越来越多,而且有越来越多的新先进技术通过实现快速开关、降低热阻与提高可靠性来提高产品价值。

器件技术

SiC 肖特基二极管销售额占了 SiC 销售额的 50% 以上,其中大部分是 650V、1200V 和1700V 等级。650V 二极管用于计算机、服务器和电信电源内的功率因数校正电路 (PFC) 以及高压电池充电器内的副边整流器。1200V 和 1700V 二极管用于太阳能升压电路、变换器、焊接和工业电源中的各种电路。

与硅快速恢复二极管相比,SiC 肖特基二极管的 QRR 下降更大,从而使得硬开关连续导电电路中的半桥电路或斩波电路开关的 EON 损耗降低。由于纯肖特基二极管在雪崩和正向浪涌条件下的不足,大部分制造商都提供 JBS 二极管,并添加了 PN 结,既将肖特基界面屏蔽于高场之外,以降低漏电,又改善雪崩稳定性,同时允许在浪涌条件下实现 PN 结双极注入从而降低前向压降。

一般而言,SiC 二极管的浪涌能力要远远低于硅快速恢复二极管,很大一个原因是在浪涌条件下有很大的开态压降。对于硅而言,该压降可能只有 1-2V,而对于 SiC 而言,可能达到 4-6V。由于 SiC 二极管晶粒要小得多,这种情况带来了散热挑战。制造商采用圆片减薄技术来降低开态压降,并降低热阻。TO 和 DFN 封装中采用了先进的晶粒粘接方案,如银 (Ag) 烧结,从而最大程度减少热阻和阻止在浪涌条件下融化,而融化在传统结中非常常见。这种特性能在约 8-12 倍额定电流下提供充足浪涌能力。

从成品和电流额定值看,UnitedSiC 有 100A,1200V 和 200A,650V 两种二极管可用于功率模块中。还有多种符合 AEC-Q101 要求的银烧结(无 Pb,环保)二极管,可以用于汽车应用。

SiC 晶体管技术

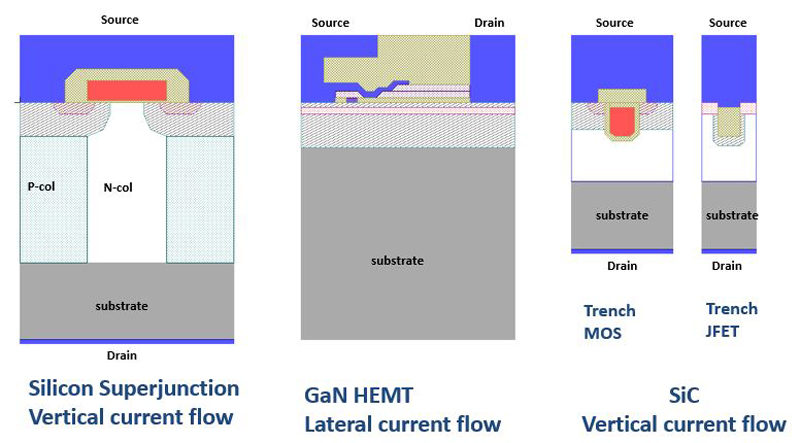

图 1 显示的是用于功率转换的 650V 高性能 FET 的占市场主流的主要器件结构,氮化镓 (GaN) HEMT(高电子迁移率晶体管)是其中唯一的两个源级端子都在晶片上表面的横向器件。硅基超结器件运用电荷平衡原理,其中,相等的 N 柱和 P柱掺杂质使得总净电荷基本为零,因而可以快速消耗电压支持,即使为了降低电阻而对 N 柱进行大量掺杂也是如此。2000 年至 2018 年,单位面积采用的 N 柱有所增加,从而帮助将导通电阻降低到了传统无电荷平衡的硅限制的近十分之一。硅基超结技术的年销售额超过 10 亿美元,单位面积导通电阻 (RdsA) 值低至 8mΩ-cm2,处于行业前沿,而其他技术的单位面积导通电阻 (RdsA) 值为 12-18mΩ-cm2。GaN HEMT 现在的开关行为非常出色,它的 RdsA 目前处于 3-6mΩ-cm2 范围内。这些横向器件构建在硅衬底上,该衬底比 SiC 衬底便宜很多,但是目前的 GaN 器件仍比 Si 器件贵很多。现在还有 650V 的 SiC 沟槽式和平面式 MOSFET,其 RdsA 范围为 2-4mΩ-cm2。UnitedSiC 第 2 代沟槽式 JFET (UJC06505K) 的 RdsA 值达到了 0.75mΩ-cm2。这意味着 SiC JFET 晶粒体积可以达到硅晶粒的七分之一至十分之一,甚至可以远远小于 GaN 或 SiC MOSFET 结构。如果以实现与硅器件同成本为目标,这一点十分重要。

图 1:硅基超结、GaN HEMT、碳化硅(SiC 平面式或沟槽式 MOSFET)和 SiC 沟槽式 JFET(结型场效应晶体管)中最常用的 650V 晶体管器件体系结构。大部分功率器件都是垂直的,为大电流电极提供空间。GaN HEMT 为横向器件,两个功率电极都位于上表面

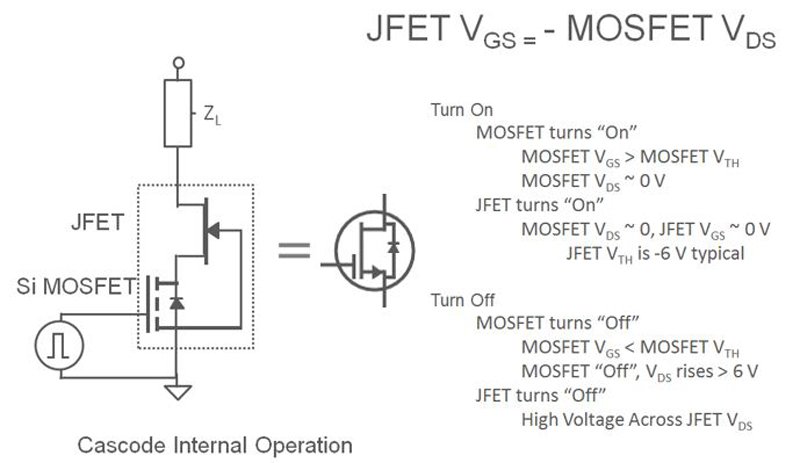

UnitedSiC FET 使用图 2 所示的共源共栅结构,将低成本的 25V 硅 MOSFET 与常开 SiC JFET 封装到一起,形成可以与任何常关 MOSFET、IGBT 或 SiC MOSFET 一同使用的器件。该器件在续流二极管模式下的行为非常出色,并且无需将反向并联硅快速恢复二极管与 IGBT 或 SiC 肖特基二极管联用。

图 2:在 UnitedSiC 共源共栅 FET 中,一个 25V 硅 MOSFET 与 SiC JFET 一同封装,实现了常关运行,简化了栅极驱动,使得寄生二极管行为十分出色。该器件可以插入现有硅 MOSFET 和 IGBT 插槽,还能与所有类型的 SiC MOSFET 互换

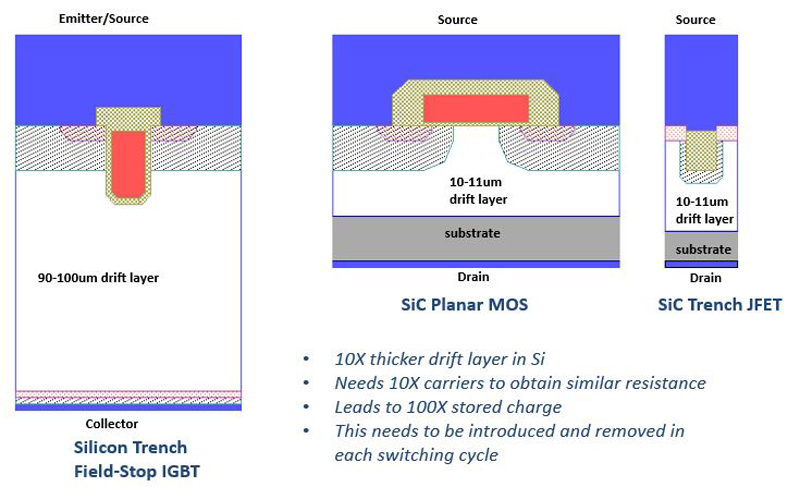

图 3 比较了 IGBT、SiC MOSFET 和沟槽式 JFET 的结构。IGBT 是双极器件,打开时拐点电压为 0.7V,达到拐点电压之后,由于电荷载流子注入,宽电压阻拦层的电阻降低。因为必须去除这些载流子才能让器件返回阻拦状态,所以会有不可见的“开关”损耗,且损耗远远大于采用 SiC MOSFET 造成的损耗。在这种情况下,UnitedSiC 共源共栅产品的碳化硅单位面积电阻极低,甚至可以直接插入 IGBT 插槽中而无需更改栅极驱动,从而获得更好的能效。如上篇文章所述,SiC MOSFET 和 SiC Cascode FET 导电过程中没有拐点电压,因而即使在低频应用中也能提高能效。

图 3:在 1200V 及更高电压下,采用硅时最常见的器件结构是电场终止型 IGBT。图中还显示了 SiC MOSFET 和 SiC 沟槽式 JFET 的结构。SiC 器件采用厚度只有十分之一的电压阻拦层以及 100 倍高的掺杂度,从而实现低电阻。硅 IGBT 通过在开态中注入存储的电荷来降低电阻,且在每次开关循环中必须加载和去除电荷

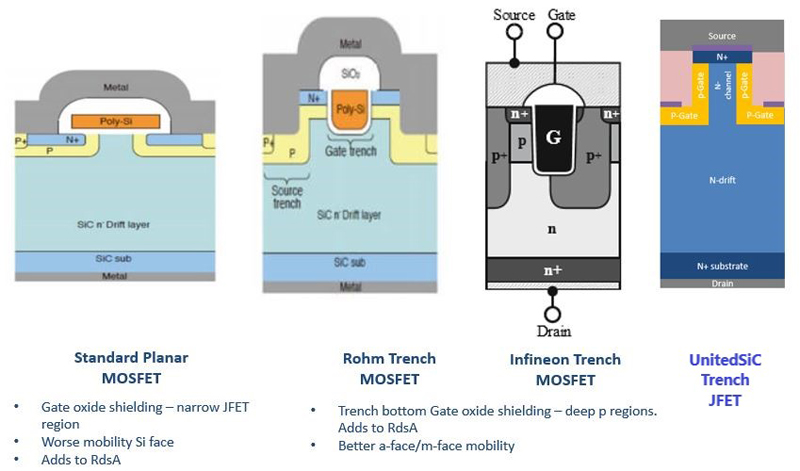

图 4 深入介绍了目前市场上的各种 SiC 晶体管方案。大部分供应商提供 SiC 平面式 MOSFET,还有一部分推出了沟槽式 MOSFET。所有 SiC MOSFET 的沟道迁移率都差(大约比硅差了 15-30 倍),但是由于沟道的晶体定向,沟槽式 MOSFET 的迁移率比较好。沟槽式 JFET 有一个迁移率非常高的体沟道,使得额定电压为 650V-1700V 的器件中单位面积的电阻较低。

图 4:SiC 平面式和沟槽式 MOSFET 以及 SiC 沟槽式 JFET 的器件结构。MOSFET 的栅氧化层下有一个沟道,可通过给栅极施加电压感应到。JFET 沟道在无电压的情况下也存在,可以通过对栅极-源级 PN 结施加反相偏压而掐断。沟槽式 JFET 中的低电阻是由体沟道带来的,无需将栅氧化层屏蔽在高场强之外

SiC 器件的运行电场的场强通常是硅器件的 10 倍,这是由厚度只有硅器件十分之一的基础电压支持层造成的。虽然这对 JFET 等体沟道器件不构成问题,但是对于 MOSFET 中的氧化物/SiC 界面处而言,必须仔细注意,避免各种程度的氧化应激,因为氧化应激可能导致运行寿命缩短或故障率过高。在平面式和沟槽式 JFET 中,通过屏蔽栅氧化层来管理电场会不可避免地导致导通电阻的进一步提高。

SiC JFET 电阻现在非常低,在所有 650V 等级器件中以及 30-40% 的 1200V 等级器件中,器件所用的 SiC 衬底的电阻占了总电阻的 50% 以上。为此,晶片的厚度从开始的 350um 降至 100-150um,并使用专利方法形成激光辅助的背面触点。推广这种技术并改进单元设计预计会将导通电阻进一步降低至 0.5mΩ-cm2 (650V) 和 1.0mΩ-cm2 (1200V)。因此,本就因迅速扩大的产量而降低的 SiC 成本很可能会因这些技术改进而进一步降低。

现在生产的大部分晶片都是 6 英寸晶片,8 英寸晶片的生产工作也已经开始了。少数额定电流为 100A-200A 的器件现已有售。UnitedSiC 现在生产 9mohm,1200V 堆叠式共源共栅芯片 (5.7x6.3mm) 和 5.7m,1700V 芯片 (8x8mm)。这些大电流器件可以通过降低并联所需器件数量来简化大电流模型。

封装技术

SiC 器件即可作为独立器件提供也可在需要大功率电平时置于功率模块中。目前的市场主流产品为独立的功率器件,不过模块的市场份额正在迅速增长。

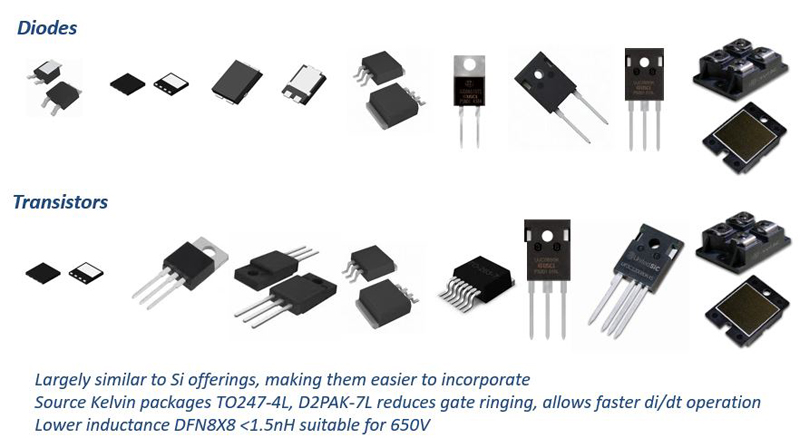

图 5 显示了 SiC 二极管和晶体管的各种可用独立封装。UnitedSiC 在不断迅速增加封装类型,为功率电路设计师提供他们所需的能满足系统约束的各种选择。几乎所有这些封装都是众所周知的行业标准封装,与硅器件配合使用且应用广泛。虽然封装的形状系数保持不变,但是内部可以添加许多增强功能,以更好地利用 SiC 器件的能力。

图 5:SiC 二极管和晶体管的典型可用封装选项系列,额定功率从左到右依次递增。2A 至 200A 器件有独立外形。由于支持非常快的开关速度,源级开尔文封装会让 SiC 晶体管表现突出

几乎所有的 UnitedSiC 二极管和晶体管都使用银烧结的方式将 SiC 晶粒粘接到引脚框架上。在使芯片变得更薄的同时,这种方式还能帮助克服由于芯片体积变小产生的热阻难题。

近期推出的 SiC TO247-4L、D2PAK-7L 和 DFN8x8 器件可帮助克服部分栅极驱动问题,这些问题与快速开关和使用更成熟的 D2PAK-3L、TO220-3L 和 TO247-3L 等有大型常见源级电感的封装相关。虽然传统的 3 引脚封装是工业领域的主力产品,但是它正在让位于“开尔文源级”封装,因为这种封装支持更加清晰和快速的开关且影响很小或者没有影响。

共源共栅器件对因修改栅极电阻造成的短暂关闭的控制能力通常十分有限,尤其是在延迟时间较长并导致电路运行干扰时。为管理这一点,UnitedSiC 提供了具有不同速度范围的器件,器件内部经过预先调整,以适应某个最大开关速度(UJ3C 和 UF3C 系列)。如果电路经受过渡电压过冲或电源环路振铃,则采用小 RC 缓冲电路会非常有效,且能将耗损影响减到最低。UnitedSiC 网站上提供了用户指南,为用户提供了栅极驱动和缓冲电路建议,让器件更易用。

鉴于相比硅器件,SiC 器件的电流密度越来越大,从顶部源级端子提取电流的封装技术也在不断进步。铝条带键合、使用铜缓冲的粗铜引线键合、使用铜夹的无接线封装等都是能够延长独立封装和功率模块中的 SiC 晶体管功率循环寿命的重要新兴方法。

预计嵌入式封装能让低电感体系结构未来有更大改善空间,甚至能整合驱动器和电容,从而通过尽可能降低电感来提高快速开关效率。

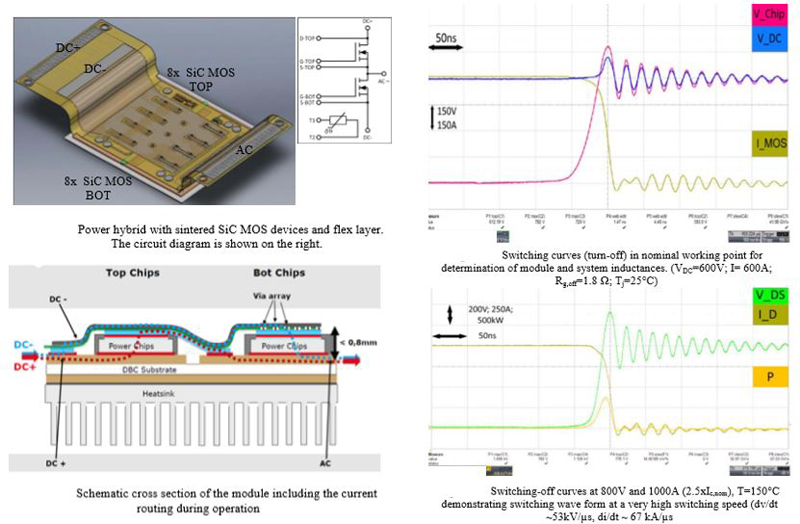

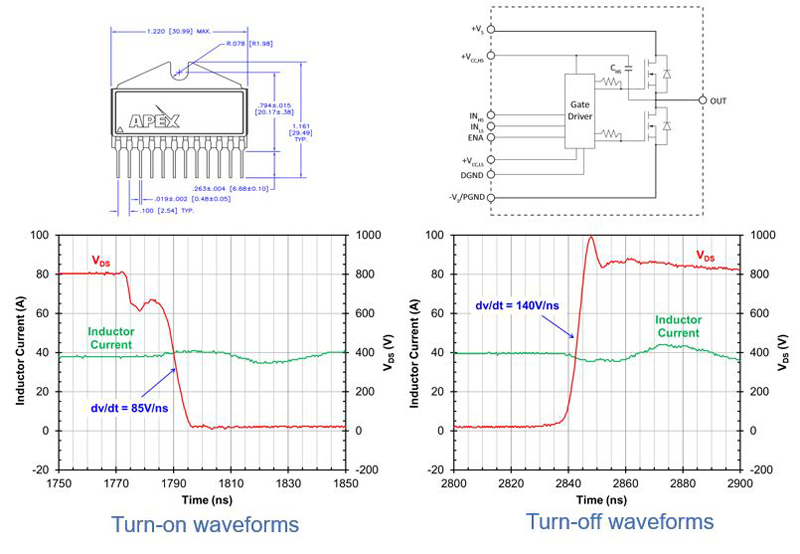

许多功率模块正在纷纷涌入市场,包括 Easy-1B/2B 这样的较小模块和标准 IGBT 中的较大模块,如 34mm 和 62mm 占板空间以及 Econodual 样式模块。在电动车逆变器方面,许多技术正在针对 SiC 进行优化,包括带翅片式散热器的混合封装式模块和双面冷却选项。图 6 显示的是 Semikron 提出的超低电感模块,它能实现非常快的开关速度且过冲电压可控。图 7 显示的是 Apex 制造的含半桥驱动器和 FET 的 SIP 模块,及其在使用 UnitedSiC 35mohm,1200V 堆叠式共源共栅产品时的相应高速开关波形。

图 6:2017 年 Semikron 展示的 400A,1200V 模块,其回路电感仅为 1.4nH。磁通相抵的低电感设计有助于 SiC 充分发挥开关速度的优势,可在系统层面上实现性能提高和成本降低

图 7:含 UnitedSiC 35m,1200V 堆叠式共源共栅器件和内置半桥驱动器的 SIP 模块,正在 40A,800V 且上升和下降时间极短的条件下进行开关工作。虽然采用紧凑的高频设计,但是这种进步不仅让使用高速器件变得更简单,而且由于缩小了无源器件,系统层面获得了很大的成本优势

人们一直认为,SiC 器件会对电压较高的应用产生很大影响。首批位于 XHP 型占板空间中的 3300V 和 6500V 模块现已发布,而 10kV 模块也即将诞生。UnitedSiC 利用超共源共栅技术这一独特方法进入此领域,它将 1700V 低电阻器件串联,打造电压更高的器件,且所有器件都由位于末端的一个低压 FET 控制。已证实该方法具备很高的可扩展性,能实现 3300V – 20kV 的模块,而无需高压芯片。这对高压固态断路器和实施连接到中压电网的固态变压器都非常有用。

结论

SiC 器件和封装技术还在继续快速发展,促使在许多快速发展的终端市场应用中的市场采用率不断提高。这将推动许多不同方向的新宽带隙产品开发,如用于直流转换的极高速开关器件、电动车车载充电器、服务器电源、电感损耗非常低的电动车逆变器模块。大量拥有这种改进的宽带隙器件能力的新一代系统设计目前正处于开发阶段,SiC 技术必将使得市场上的整体功率性能和能效更上一层。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码