Achronix推出的领先业界的全新一代FPGA芯片产品及解决方案

近年来,大数据、云计算、物联网等技术发展迅速,而5G、人工智能等新兴技术也将迎来新的发展,这些变化也给FPGA带来了绝佳的发展机遇。2018年11月27日,由业内公认的领先的半导体企业Achronix Semiconductor主办的Achronix Speedcore7t新产品发布会在北京成功举办,此次发布会主要介绍了公司新推出的领先业界的全新一代FPGA芯片产品及解决方案,以及该公司最新的中国市场进展和策略,并且接受了媒体采访。本次发布会的主讲人是Achronix Semiconductor公司市场营销副总裁Steve Mensor先生。

Achronix Semiconductor公司市场营销副总裁 Steve Mensor

Steve先生首先介绍了一下Achronix公司的基本情况、发展历程和市场地位。Achronix Semiconductor公司成立于2004年,是一家私有的、采用无晶圆厂模式的半导体公司,总部位于美国加利福尼亚州圣克拉拉市,提供了高性能的现场可编程逻辑门阵列(FPGA)解决方案。Achronix的发展历程,就是作为核心力量之一不断地推动高性能FPGA市场向前发展的过程。Achronix长期以来在可编程逻辑领域总是不断创新,为业界树立了领先性能、功耗和成本的标准。其Speedcore嵌入式FPGA IP成为业界唯一经过流片验证过的嵌入式FPGA技术。

Steve先生介绍Achronix公司

Steve先生认为,由于摩尔定律的放缓以及一些其他因素的影响,当前阶段处理器性能的提升已经愈发困难。为了满足各行各业不断增加的计算需求,就需要针对特定应用和数据集的架构。人工智能拥有强大的数据运算能力、传输存储能力,但同时对成本和功耗能效等提出新要求,如何处理这些问题需要从工艺来着手,核心架构的研发创新以及多种工具的支持,先进制程工艺都可以让芯片性能得到提高,并且功耗也会更低,也就是将其专业化。就目前的市场来说,大部分的FPGA芯片都是基于20nm和28nm的工艺,但是现在人工智能发展迅速,包括2019年的5G技术,对芯片的要求有了很大的提高,16nm甚至7nm的工艺才能满足其需求。在这种情况下,工艺技术领先的FPGA公司就取得了先机,Achronix公司凭借其FPGA的硬件加速器器件和高性能嵌入式FPGA半导体知识产权(eFPGA IP)一直以来都走在FPGA工艺技术的前列,面对即将到来的新兴技术对于FPGA技术的需求,他们也是成竹在胸。

《电子产品世界》记者在采访Steve先生时获悉,Achronix公司即将推出的用于人工智能/机器学习(AI / ML)和网络硬件加速应用的第四代Speedcore eFPGA IP,这款新一代的 Speedcore 7t在TSMC 7nm上构建,可以提供最佳的性能和面积以及更低的功耗,更有助于提升计算、数据传输和存储带宽的性能。与前一代Speedcore eFPGA产品相比,Speedcore Gen4的性能提高了60%、功耗降低了50%、芯片面积缩小了65%。同时,新的机器学习处理器(MLP)单元模块可为人工智能/机器学习(AI/ML)应用提供高出300%的性能。

Steve先生表示,在这个新的Speedcore Gen4架构中,Achronix将机器学习处理器(MLP)添加到Speedcore可提供的资源逻辑库单元模块中。MLP模块是一种高度灵活的计算引擎,它与存储器紧密耦合,从而为人工智能和机器学习应用提供了性能/功耗比最高和成本最低的解决方案。Achronix正在使用经过验证的同样的方法体系来为客户提供最新的Speedcore Gen4 eFPGA技术,来满足他们将eFPGA IP的所有优势和灵活性与增强的人工智能/机器学习功能相结合的愿望,而这种最前沿的人工智能/机器学习功能得益于Achronix最新机器学习处理器单元模块和台积电(TSMC)最先进的7nm工艺技术。

接下来Steve先生向媒体记者们详细介绍了这款Speedcore Gen4新架构的具体优势及其实现过程。

架构性创新提高系统性能

与上一代Speedcore产品相比,新的Speedcore Gen4架构实现了多项创新,从而可将系统整体性能提高60%。其中查找表的所有方面都得到了增强,以支持使用最少的资源来实现各种功能,从而可缩减面积和功耗并提高性能。其中的更改包括将ALU的大小加倍、将每个LUT的寄存器数量加倍、支持7位函数和一些8位函数、以及为移位寄存器提供的专用高速连接。

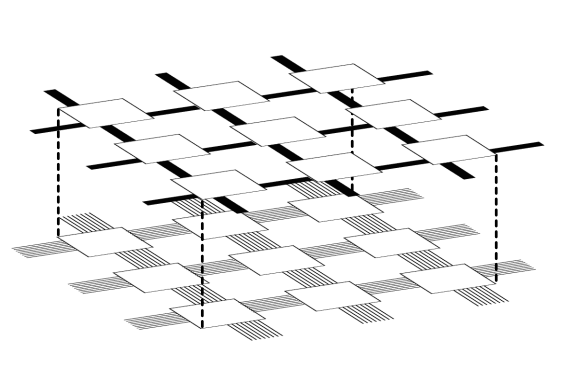

Steve先生强调说,Speedcore Gen4其中的路由架构也借由一种独立的专用总线路由结构得到了增强,由于该路由结构中还有专用的总线多路复用器,可有效地创建分布式的、运行时可配置的交换网络。这样就可以为高带宽和低延迟应用提供最佳的解决方案,并在业界首次实现了将网络优化应用于FPGA互连。

最新一代高速布线架构

解决带宽爆炸问题

Steve先生还表示,固定和无线网络带宽的急剧增加,加上处理能力向边缘等进行重新分配,以及数十亿物联网设备的出现,将给传统网络和计算基础设施带来压力。这种新的处理范式意味着每秒将有数十亿到数万亿次的运算。传统云和企业数据中心计算资源和通信基础设施无法跟上数据速率的指数级增长、快速变化的安全协议、以及许多新的网络和连接要求。传统的多核CPU和SoC无法在没有辅助的情况下独立满足这些要求,因而它们需要硬件加速器,通常是可重新编程的硬件加速器,用来预处理和卸载计算,以便提高系统的整体计算性能。经过优化后的Speedcore Gen4 eFPGA已经可以满足这些应用需求。

Speedcore Gen4是最佳的人工智能/机器学习加速器

由于应用了新的网络架构技术,人工智能/机器学习还对高密度和针对性计算产生了显著增加的需求。与以前的Achronix FPGA产品相比,新的Achronix机器学习处理器(MLP)利用了人工智能/机器学习处理的特定属性,并将这些应用的性能提高了300%。这是通过多种架构性创新来实现的,这些创新可以同时提高每个时钟周期的性能和操作次数。

通过投影,Steve先生向到场媒体记者们展示了新的Achronix机器学习处理器(MLP)是一个完整的人工智能/机器学习计算引擎,支持定点和多个浮点数格式和精度。每个机器学习处理器包括一个循环寄存器文件(Cyclical Register File),它用来存储重用的权重或数据。各个机器学习处理器与相邻的机器学习处理器单元模块和更大的存储单元模块紧密耦合,以提供最高的处理性能、每秒最高的操作次数和最低的功率分集。这些机器学习处理器支持各种定点和浮点格式,包括Bfloat16、16位、半精度、24位和单元块浮点。用户可以通过为其应用选择最佳精度来实现精度和性能的均衡。

为了补充机器学习处理器并提高人工智能/机器学习的计算密度,Speedcore Gen4查找表(LUT)可以实现比任何独立FPGA芯片产品高出两倍的乘法器。领先的独立FPGA芯片在21个查找表可以中实现6x6乘法器,而Speedcore Gen4仅需在11个LUT中就可实现相同的功能,并可在1 GHz的速率上工作。

Steve先生最后表示,采用台积电7nm工艺节点的Speedcore Gen4,主要针对当下新兴人工智能/机器学习和高数据带宽应用的爆炸式需求。同时,在未来发展中,计算加速度、网络加速、5G、智能驾驶、人工智能等都是他们的目标市场,因为这些市场都对高性能FPGA有着强烈的需求,Achronix公司也能最大程度地满足它们的需求。Achronix公也宣布将于2019年上半年开始提供适用于台积电7nm工艺的第四代Speedcore eFPGA IP,这也意味着7nm eFPGA的设计将最大限度地应用在快速发展的AI中,eFPGA架构创新也能为人工智能加速。

关键词: Achronix FPGA Speedcore Gen4

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码