一个简单的PCI总线INTx中断实现流程

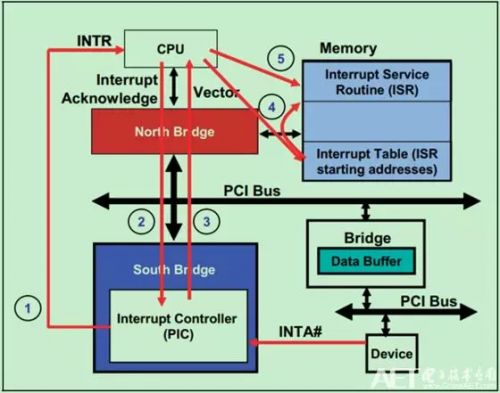

一个简单的PCI总线INTx中断实现流程,如下图所示。

1. 首先,PCI设备通过INTx边带信号产生中断请求,经过中断控制器(Interrupt Controller,PIC)后,转换为INTR信号,并直接发送至CPU;

2. CPU收到INTR信号置位后,意识到了中断请求的发生,但是此时并不知道是什么中断请求。于是通过一个特殊的指令来查询中断请求信息,该过程一般被称为中断应答(Interrupt Acknowledge);

3. 该特殊指令被发送至PIC后,PIC会返回一个8bits的中断向量(Interrupt Vector)值给CPU。该中断向量值与其发送的INTR请求是对应的;

4. CPU收到来自PIC的中断向量值后,会去其Memory中的中断向量表(Interrupt Table)中查找对应的中断服务程序(Interrupt Service Routines,ISR)在Memory的位置;

5. 然后CPU读取ISR程序,进而处理该中断。

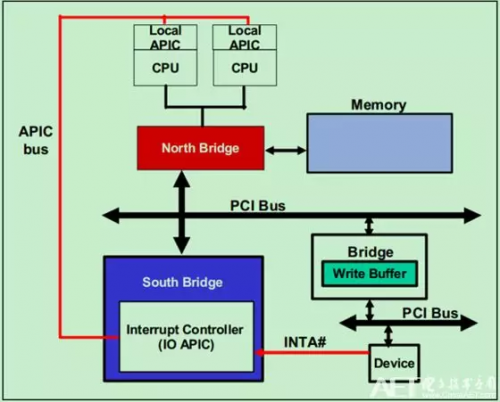

上面的例子主要是基于早期的单核CPU设计的,并没有考虑到目前多核CPU的情况。因此,在后续的PCI Spec中,将PIC替换为IO APIC(Advanced Programmed Interrupt Controller)。如下图所示:

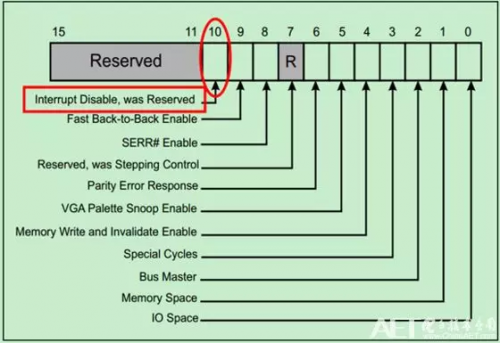

实际上,在PCIe总线中,传统的中断机制(INTx)已经很少被使用,很多应用甚至直接将该功能禁止了。无论是在PCI总线(V2.3及以后的版本),还是PCIe总线中,都可以通过配置空间中的配置命令寄存器(Configuration Command Register来禁止INTx中断机制),如下图所示。不过,需要特别注意的是,虽然该bit的名称为中断禁止(Interrupt Disable),但是其只会影响INTx,对MSI/MSI-X不会造成影响。因为MSI/MSI-X的使能(或禁止)是通过配置空间中的MSI/MSI-X Capability Command Register来实现的,并且一旦使能了MSI/MSI-X,PCI总线/PCIe总线便会自动地禁止INTx。

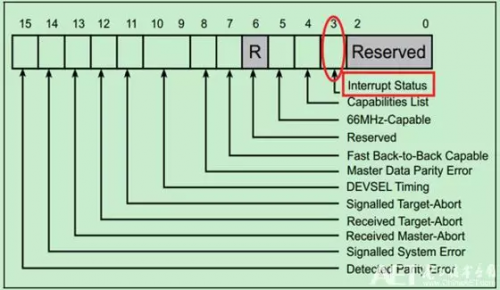

并且可以通过配置状态寄存器的中断状态(Interrupt Status)bit来确定当前的中断状态,如下图所示:

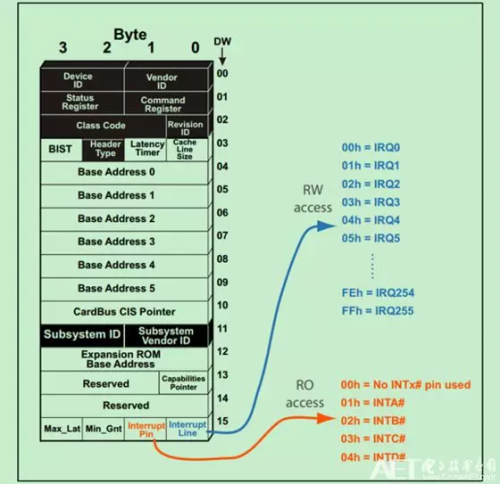

INTx相关的寄存器在配置空间的位置如下图所示,Interrupt Pin和Interrupt Line分别定义了中断边带信号引脚号(INTA#~INTD#)和中断向量号(IRQ0~IRQ255)。

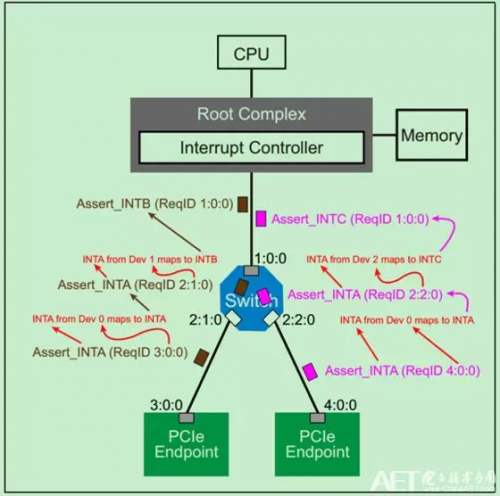

然而,PCIe总线继承了PCI总线的INTx中断机制,但是在实际的PCIe设备之间的中断信息传输中使用的并非边带信号INTx,而是基于消息(Message)的。其中Assert_INTx消息表示INTx信号的下降沿。Dessert_INTx消息表示INTx信号的上升沿。当发送这两种消息时,PCIe设备还会将配置空间的相关中断状态bit的值更新。对于PCIe-PCI(X)桥设备来说,会将接收到的来自PCI/PCI-X总线的INTx信号转换为消息,在往上级发送。一个简单的例子如下图所示:

INTx消息的格式为:

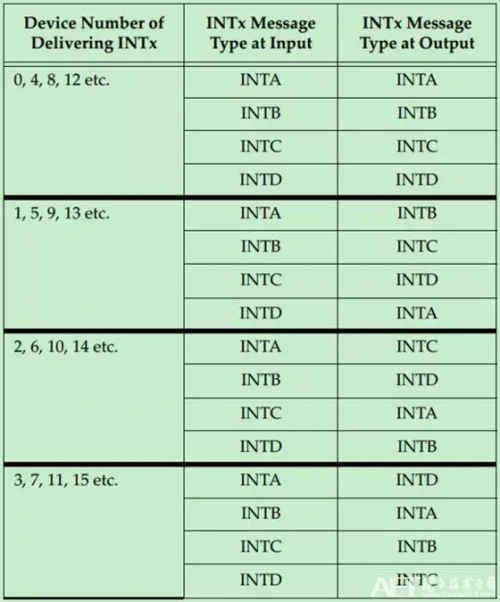

桥设备中的INTx消息的类型与设备号的映射关系如下图所示:

对应的,一个简单的例子如下:

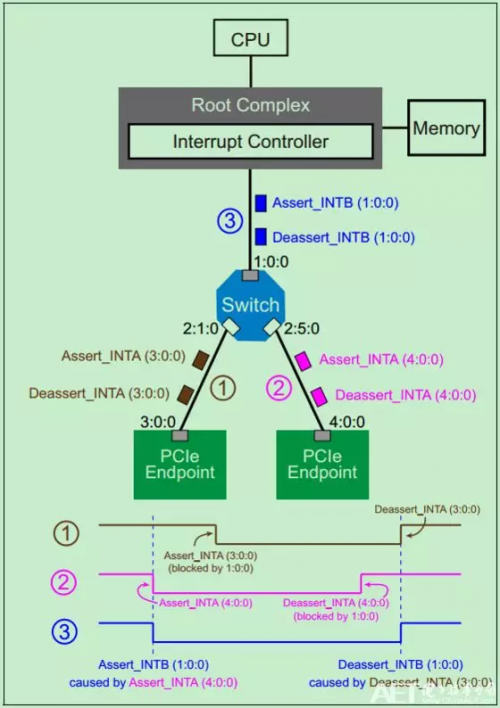

当多个设备使用同一个中断信号线时,只有先置位的设备会被中断控制器响应。但是该中断信号线,并不会因为其中一个设备的中断请求得到响应便被清除,而是会等到所有的发送请求的设备的中断请求都得到了响应之后。如下图所示:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码