基于软件的空间辐照下FPGA可靠性设计方法

FPGA以其集成度高、灵活性强、开发周期短的特点,在航天领域得到了越来越广泛的应用。然而,其工作的空间环境存在着大量γ光子、辐射带电子、高能质子等高能粒子。这些高能粒子轰击到器件上,会产生总剂量效应(Total Ionizing Dose, D)、单粒子翻转(Single Event Upset, SEU)、单粒子锁定(Single Event Latchup, SEL)、单粒子烧毁(Single Event Bumout,SEB)、单粒子栅击穿(Single Event Gate Rupture, SEGR)、内带电效应等空间辐射效应[1]。这些效应对基于SRAM的FPGA的影响尤为明显。

现代FPGA工艺向着低电压、高集成度方向发展,这使得发生空间辐射响应的阈值越来越低,发生故障的概率越来越大。空间辐射效应的发生,轻则会使设备工作异常,重则会导致设备烧毁、永久失效。因此,FPGA必须进行高可靠性设计,来最大限度地预防和解决空间辐射效应的影响。

1 空间辐照效应

据卫星资料统计,其异常记录中有70%是由空间辐射环境引起的[2]。主要空间辐射效应与辐射源及作用对象之间关系如表1所列。

表1 主要辐射效应、辐射源及对象

单粒子效应(Single Event Effect,SEE)是单个高能质子或重离子入射电子元器件上引发的辐射效应。根据效应的机理不同可分为单粒子翻转、锁定、烧毁、栅击穿等。

当单个空间高能带电粒子轰击到大规模、超大规模的逻辑型微电子器件时,沿粒子入射轨迹,在芯片的PN结附近区产生电离效应,生成一定数量的电子空穴对(载流子)。如果芯片处于加电状态,这些由于辐射产生的载流子将在芯片内部电场作用下发生飘移和重新分布,从而改变了芯片内部正常载流子的运动分布和运动状态。当这种改变足够大时,将引起器件电性能状态的改变,造成逻辑器件或电路的逻辑错误,例如:存储器中数据发生翻转,使能信号被重新置位,从而引起逻辑功能混乱、计算机程序“跑飞”,甚至造成灾难性的后果。

目前,大多数FPGA基于SRAM结构。基于SRAM的FPGA中的基本可编程通孔是一个1位的SRAM单元。这种SRAM通孔的编程和擦写方式与其他SRAM存储器一样。虽然SRAM通孔比一般SRAM组建更可靠,但之后的状态也很容易被空间辐射产生的电荷改写[3]。

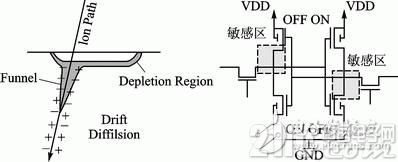

图1为与FPGA相同的CMOS工艺单粒子翻转示意图和单粒子翻转敏感区域[4]。

图1 与FPGA相同的CMOS工艺单粒子翻转示意图

因此,对于FPGA软件设计而言,单粒子翻转对FPGA内部逻辑、存储器的影响尤为严重,需要进行安全可靠性设计。

2 防范措施

通常可以采用如下的方法,最大限度地防止或避免空间辐照下的单粒子效应对FPGA软件的影响。

2.1 定期重新配置FPGA

对FPGA进行重新配置,可以清除积累的任何错误。设计者必须确定潜在错误的影响,以及这些错误蔓延所需的时间。在这个时间段之内重新配置FPGA,或者设计检测电路,当FPGA工作错误时,及时对FPGA进行重新配置。虽然错误仍然会蔓延,但潜在的损害被重新配置所限制。

笔者所设计的系统为CCD相机成像系统,由任务需求及功能估算,每次开机上电时间约为120 s。开机即加载FPGA逻辑,摄像任务完成后,随即下电,准备下一次摄像任务。因此,可以极大地避免空间辐照效应对设备的影响。

2.2 三模冗余(TMR)

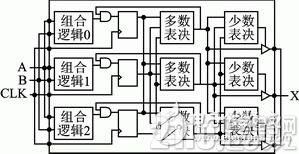

对关键信号,数据进行冗余设计,是防止SEU发生的比较行之有效的方法。冗余设计是用多个相同单元构成并联形式,最后通过表决单元输出最终的数据或信号,三模冗余是常用的冗余设计方法。理论上,在FPGA中某一单元发生SEU的概率是存在的。但连续两个相同单元同时发生SEU事件,在有限的工作时间内,几乎是不可能的。虽然一个单元发生SEU导致错误,但其他单元不会同时发生错误,通过表决,保证了数据或信号的安全可靠。图2为Xilinx公司推荐的三模冗余结构。虽然TMR带来了可靠性的提高[5],但是随之带来了系统最高运行速度的降低和资源的浪费,而且表决器本身也可能出错,并不具备抗空间辐照的能力。如果系统长时间加电工作于空间辐射环境中,由于SEU的累积效应,两个或多个表决单元都发生SEU的可能还是存在的,这就需要采取相应的设计方法,检测发生SEU的逻辑单元,将其重新置位,“拉”回正常工作状态,从而保证系统的安全可靠。

图2 Xilinx公司推荐的三模冗余逻辑

目前,Xilinx公司等FPGA制造商能够提供相应的TMR模块IP核,但目前还无法获得。可以根据实际情况,对系统关键的部位,进行三模冗余设计。

笔者在所设计的系统中,同时设计了3个“关键数据解析”单元,将解析到的关键数据同时存储在相邻的3个块RAM中,最后通过“关键数据表决单元”,输出可靠的关键数据。

2.3 周期擦除技术

周期擦除技术是指,在固定时间周期内,对系统内部各关键单元进行周期擦除复位,这样可以很大程度地避免单粒子翻转对系统产生的影响。

当系统中发生单粒子翻转事件时,可能会导致关键寄存器、计数器或关键使能信号等发生意外翻转,引起外围控制器件异常工作。若这种异常的工作状态持续时间较长,会导致设备无法正常工作甚至永久损坏。若系统采用周期擦除技术,一旦发生SEU,周期复位信号可以在很短的时间内,将错误的计数器、存储器复位到正确状态,保证系统的安全稳定。

笔者所设计的CCD成像系统,CCD探测器的各时序控制信号为关键信号。若不幸发生SEU,可能导致CCD时序驱动信号频率大幅升高,过高的频率会导致外围驱动器失效甚至烧毁。

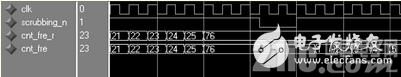

由于CCD时序控制信号为周期信号,故在时序设计中,系统内部自行产生周期擦除信号。此信号同时产生3个,进行三模冗余备份,并经过FPGA时钟树网络,保证此周期复位信号安全可靠。此信号采用同步复位,用软件仿真SEU故障,时序仿真图如图3所示。

图3 周期擦除时序仿真图

信号cnt_fre经过周期擦除处理,而cnt_fre_r未经过相应处理。可以看到,在某时刻,两个计数器均发生了SEU,计数值跳转到异常值76且保持。由于采用周期擦除技术,cnt_fre在周期擦除信号有效期间,复位至初始状态,继续正常工作。而未经周期擦除处理的cnt_fre_r则始终处于异常状态,导致系统故障。

2.4 纠错电路EDAC

FPGA系统发生SEU后,会使关键寄存器、信号等处于错误状态。尽管可以通过三模冗余技术,将这种错误状态暂时隔置,但是在长期加电工作要求的条件下,冗余单元可能继续发生错误而导致单元失效。

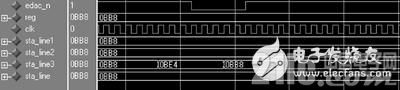

对各模块关键信号实时监测,并将检测到的错误信号及时纠正,防止了空间辐照对系统的影响。纠错电路的设计需要根据系统的特点,进行相应的设计。系统EDAC(Error Detected And Corrected)设计的功能仿真图如图4所示。

图4 EDAC功能仿真图

系统对关键寄存器Sta_Line(起始行寄存器)进行三模冗余,当纠错使信号EDAC_n有效时,进行3个冗余单元的三选二表决,并将表决结果暂存在表决结果寄存器reg内,更新至各冗余单元寄存器中。由图4可知,寄存器sta_line3在某时刻发生了SEU,sta_line3寄存器故障。在edac_n有效时,将此关键信号纠错,置回正确状态,而关键信号sta_line将始终保持正确值,保证了系统的安全可靠。

结语

可编程逻辑器件FPGA必将在航天领域得到更广泛的应用。针对空间辐照效应影响的高可靠性设计,将越来越成为FPGA软硬件设计的难点和重点。根据飞行器空间轨道的不同、辐射总剂量的差异,从硬件上,可以通过加厚屏蔽层、元器件加固等方式,尽可能地降低SEU发生的概率;从软件上,通过定期重配置、周期擦除、三模冗余、EDAC等手段,最大程度降低或消除SEU对系统的影响。本文提出的基于软件的空间辐照下FPGA可靠性设计方法,可以为空间航天FPGA嵌入式系统设计提供一定的参考。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码