DAC欠采样实现高中频信号的直接合成

0 引言

随着卫星通信速率的不断提高,高速数字调制技术得到了快速的发展,而由于后端电路及放大器的非线性,如果码率与中频的相对带宽较高,则会造成通带内频谱特性的不平坦。因此,随着码元速率的提高,中频也得相应地提高以获得更好的调制信号质量。由于中频的提高,导致了DAC采样率的提高。本文探讨了DAC在欠采样下合成高中频信号的方法,设计了对单个不甚高速的DAC,通过后端电路处理,在采样率低于奈奎斯特率的情况下,直接合成第二奈奎斯特域的高中频信号的方案。最后,对合成的信号进行了频谱分析及补偿,并且给出仿真与实验结果。

1 欠采样DAC合成高中频信号

对于高中频调制,其中一个设计难点便是DAC的高采样率问题。对于中频1800MHz,带宽960MHz的高中频信号,如果DAC采用奈奎斯特率采样并且考虑后端滤波器,则需要采样率达5.7GHz以上的DAC,这对DAC内部的采样电路有着很高的要求,并且会增加系统复杂度。

我们知道,DAC完成一次数模转换的最小时间为DAC的建立时间,为了保证数模转换的正确性,必须保证DAC的建立时间小于DAC的采样率。因此,对于高采样率的DAC,首先得减小DAC的建立时间。建立时间是由DAC内部电子开关的动作时间和运算放大器的输出电压时间所决定。所以高采样率的DAC对于内部物理器件性能的要求很高,这就使得高采样率的DAC产品比较昂贵。而市面上采样率很高的DAC也比较少,所以利用较低速率的DAC合成超奈奎斯特域的高频信号就显得尤为重要。

目前利用低于奈奎斯特采样率的DAC合成高中频信号的方法有两种:

(1)利用两个DAC输出的合成转换,等效地提高DAC的采样率,如文献中把两个DAC交错接入一个单元,混频器用作开关,可以有效地使整体采样速率增加一倍。轮流更新每个DAC,并切换到这种方式使得总的采样率从单个DAC的fs等效提高为2fs。但是这种方法受限于乘法器的速度,所以不适用于采样率很高的情况。

(2)利用低于奈奎斯特采样率的DAC对高中频信号进行欠采样,再利用第二甚至第三奈奎斯特域的频谱进行高频信号的直接合成。

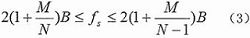

令信号的最低频率为fL,最高频率为fH,fH=NB+MB,其中N为不超过fH(fH-fL)的最大整数。为了保证带通信号的频谱镜像之间不混叠,采样频率应该大于信号带宽的两倍,并且满足以下条件:

Nfs-fH>fH (1)

Nfs-fL

故采样频率应该满足:

在欠采样时,当采样率满足式(3),便可以实现高频信号在超奈奎斯特域的合成。本设计中,中频为1800MHz,中频信号带宽为960MHz,于是有fL=1320MHz,fH=2280MHz,则N=2,M=0.376,2280

第二种方法相比于第一种方法只使用了一个DAC,节省了DAC芯片资源,但是由于超奈奎斯特域的镜像频谱相对于奈奎斯特域里的信号频谱分量会有比较大的衰减,所以造成频谱补偿的困难。本设计通过后端电路的处理,加强了超奈奎斯特域的信号强度,在优化第二种方法的基础上实现了第二奈奎斯特域的高中频信号的直接合成。

2 本设计的方案

2.1 方案概述

本设计运用了欠采样第二种方法相比于第一种方法只使用了一个DAC实现第二奈奎斯特域高中频信号合成的思想,并在其基础上做了改进。由于第二种方法相比于第一种方法只使用了一个DAC的数模转换过程是在采样时钟的控制下进行的。每到采样时钟的上升沿第二种方法相比于第一种方法只使用了一个DAC就开始新的转换,为了能用较低采样率的第二种方法相比于第一种方法只使用了一个DAC合成超奈奎斯特域的信号,我们需要利用后端电路加强信号的高频成分,以达到更好的高频信号合成质量。

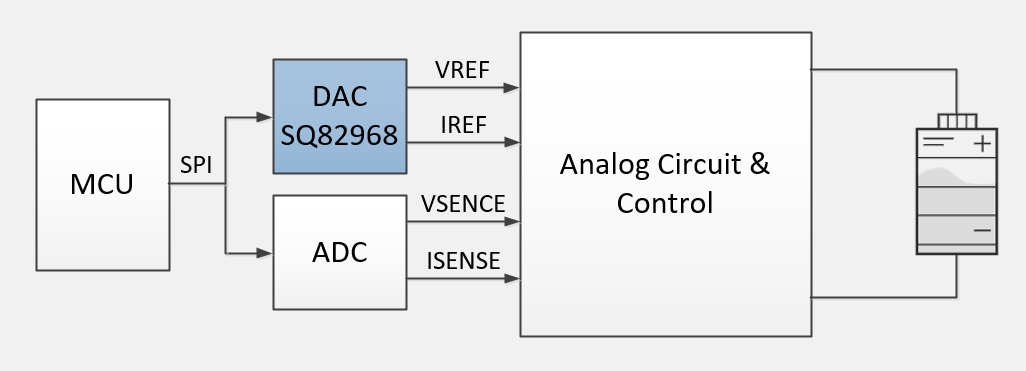

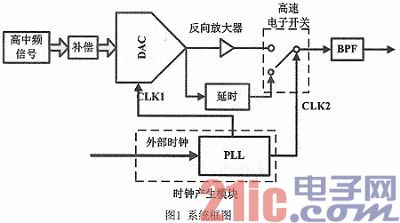

本设计的实现框图如图1所示。

其中PLL产生的CLK1为DAC的采样时钟,CLK2为高速电子开关的时钟,其中CLK2是CLK1的倍频,高中频经过DAC采样后,产生两路信号,其中一路是DAC输出信号的反相电平输出,另一路是DAC输出信号的延时,这两路信号在被CLK2驱动的高速电子开关的作用下,实现了一个周期内信号的双相电平输出。这种输出方式会带来频谱的扭曲,因此需要在数据进入DAC之前进行补偿,具体补偿方案在本节的后半部分讨论。

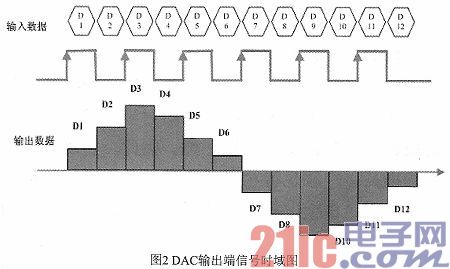

其中,DAC输出的信号时域图如图2所示。

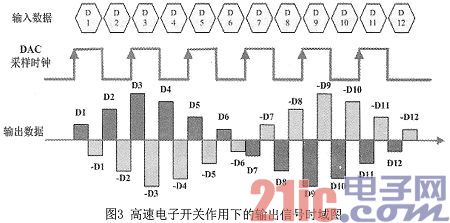

在高速电子开关作用下的输出信号为:

通过图3我们可以看出,在一个DAC采样时钟的前半个周期内输出了采样数据的正的幅值,而在后半个周期内输出采样数据的负的幅值,这样能更好地加强信号的高频成份。

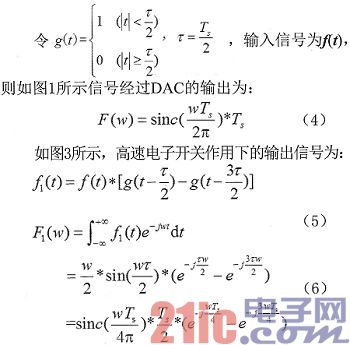

2. 2 输出信号频谱分析及补偿方案

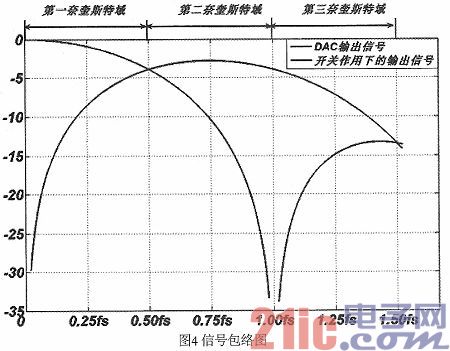

由于DAC的零阶抽样保持效应,会在通带内形成sinc包络,DAC输出信号的包络与经过开关选择后输出的信号包络如图4所示。

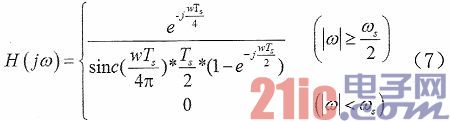

由图4我们看到,DAC输出信号的包络在3/4fs处衰减了10dB,并且关于3/4fs左右不对称,在高中频所在的第二奈奎斯特域里衰减严重。在高速电子开关作用下的双相位模式中,第二奈奎斯特域的频率分量被加强了,由DAC阶梯效应造成的信号包络的峰值在第二奈奎斯特域中,当fs为2400MHz时,1800MHz的高中频处于sinc包络的峰值处,包络关于3/4fs两边近似对称,并且在第二奈奎斯特域中频谱特性较为平坦。此时,由于半周期内信号幅度的倒转与保持效应产生的如图4所示的sinc包络,需要在DAC之前引入具有如下补偿特性的滤波器,对进行数模转换的信号预处理。滤波器的频响特性为:

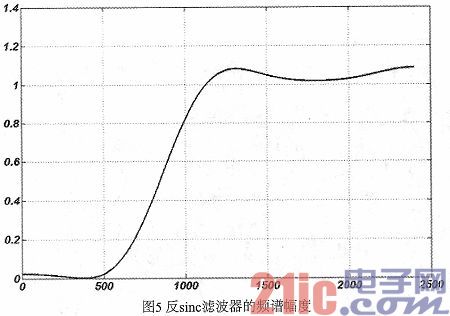

考虑到后端的带通滤波器,调制信号带宽最大为0.4*fs=960MHz,我们只关心带内的补偿即可。用Matlab生成的DAC之前的反sinc滤波器的频谱幅度为图5所示。

本设计只使用了一个DAC进行高中频信号的合成,减少了DAC芯片资源的消耗,并且通过加强第二奈奎斯特域频率分量的方式,可以降低补偿的困难,提高合成信号的质量,具有实用意义。

由于本设计的目标是实现中频1800MHz,带宽为960MHz的高中频信号,根据分析,设计了DAC的后端电路,实现信号一个采样周期内的双相位输出,用采样率为2400MHz的DAC实现了第二奈奎斯特域的高中频信号的直接合成。对于不同的需求,可能有不同的方法选择,而事实上,还能通过开关电路实现归零码或者调节输出的不同占空比,来适应特殊环境下的需求,这点在文献中有说明。

3 仿真与实验结果分析

本设计采用QPSK调制,码元速率为710MSPS,经过星座图映射,0.35成形,插值后的I、Q两路基带信号带宽为480MHz,与数字NCO产生的1800MHz的数字载波相乘,形成中频1800MHz,带宽960MHz的已调信号,采样率为2400MHz。

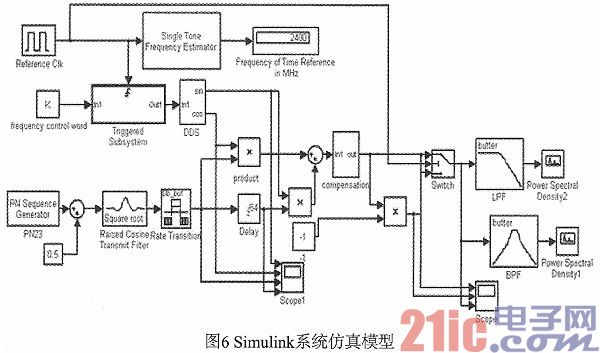

本设计的Simulink仿真模型如下:

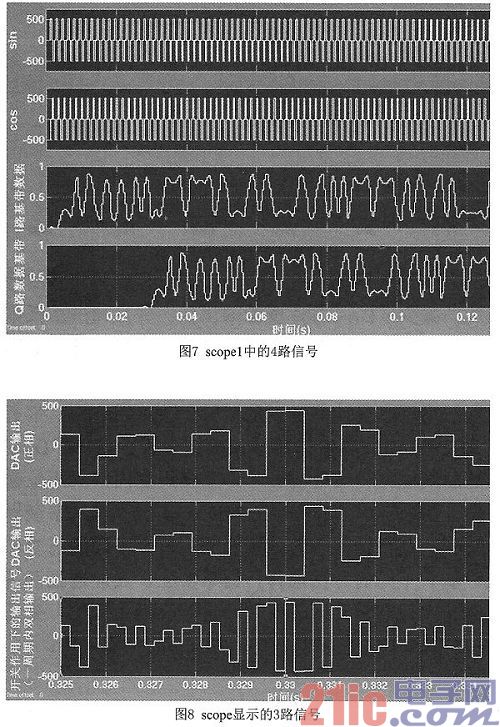

图6中的scope1显示的4路信号分别是两路正交数字载波与经过成形插值后的I、Q两路基带信号,scope1中的4路信号如图7所示。

图8是图6中scope显示的3路信号。

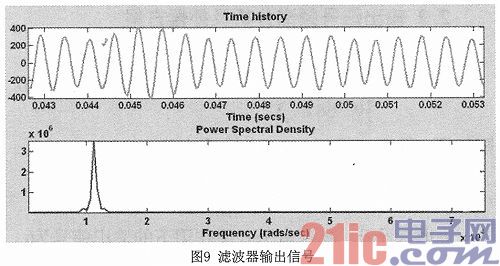

其中第一路为DAC正相输出的时域波形,第二路为DAC反相输出的时域波形,第三路是经过高速开关之后的信号时域波形。由图8我们可以看出,在开关作用下、每个DAC采样时钟周期输出了正反两个相位的信号。如图6所示,开关选择后的输出信号经过7阶的巴特沃斯带通滤波器后,可以得到第二奈奎斯特域的中频为1800MHz,带宽为960MHz的信号如图9所示。

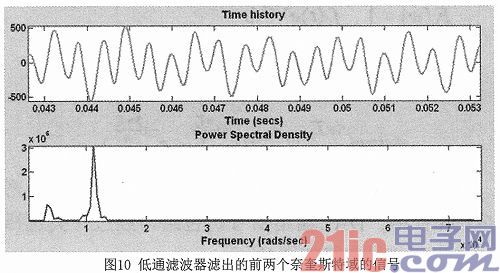

用低通滤波器滤出的前两个奈奎斯特域的信号如图10所示。

由图10可以看出,由于DAC工作在欠采样率下,存在600MHz与1800MHz两个中频的调制信号;另外,本设计利用高速开关与DAC后端电路及前端补偿,在一周期内实现信号双相输出的方案,有效地加强了第二奈奎斯特域的频率分量。图10中,由于存在两个频率分量,故时域波形表现为两种中频频率的调制信号的叠加,而图9带通滤波后,时域波形是第二奈奎斯特域的高中频调制信号。

4 结论

本文探讨了一种利用低于奈奎斯特采样率的DAC及其后端电路,实现第二奈奎斯特域的高中频直接合成的方法,给出了整体设计方案、频谱分析并提出补偿方案。在QPSK的调制模式下,进行了高中频调制信号经过本设计的DAC及其后端电路的仿真,仿真结果证明,本方案能加强第二奈奎斯特域的频谱分量,降低补偿的困难,提高合成信号的质量,在DAC的采样率低于奈奎斯特率的情况下,实现高中频信号的直接合成。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码