高速高精度多功能数据采集卡的设计

作者/代威威 董文岳 珠海欧比特控制工程股份有限公司(广东 珠海 519080)

数据采集卡是模-数信号转换与信号处理系统的关键部分。在要求不高的工控应用场合中,大多数应用采样速率均低于1 Msps的中、低速数据采集卡;采样速率高于1 Msps的高速或者超高速数据采集卡,则主要应用于要求较高的工控领域中。而PCI总线通用性与广泛性表明其在未来的十年工控领域中它仍占主导地位。高速数据采集卡目前分成两类:一种是以高采样速率采集一定深度的数据后,再把数据通过PCI总线传输给上位机,这类的采集卡由于不是即时的且并不是捕获所有的数据,因此采样速率往往可以高达100 Msps甚至200 Msps以上;另一种则是捕获所有的数据且即时显示在上位机上,这类的采集卡研发一直是工控领域研发的难点,受限于PCI带宽,采样速率国内一直并没有突破5 Msps的产品,而欧比特公司的产品具备边沿触发方式,结合上位机的虚拟示波器技术,可以实现双通道10 Msps/单通道20 Msps的全速不间断采样。

基于以上的原因,利用PLX公司PCI9056-66BA,珠海欧比特公司在超高的数据采集系统中做了一些研究,设计12 bit分辨率的超高速高精度数据采集PCI板卡EMBC2000- PCI-AD485CAN。该数据采集板卡遵循PCI 2.3标准,同时支持5 V/3.3 V 标准32位PCI接口,已实现双通道10 Msps/单通道20 Msps的全速不间断采样,且采集的数据可利用CAN或者RS485总线进行远程数据传输,满足了高端工控领域的应用要求。

1 EMBC2000-PCI-AD485CAN的硬件功能结构

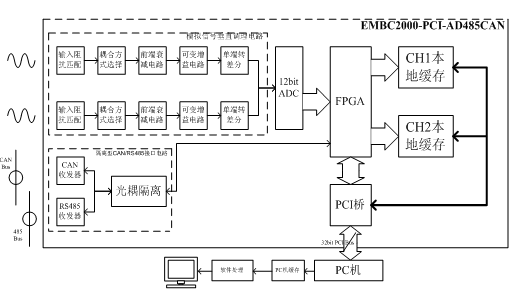

EMBC2000-PCI-AD485CAN(以下简称EMBC2000-PCI)硬件结构主要由6个部分组成:模拟信号垂直调理电路、数据采集及主控电路、本地数据缓存电路、PCI总线接口电路、隔离型CAN/RS485接口电路、电源电路,实现了双通道模拟信号输入,其结构图如图1所示。

图1 EMBC2000-PCI硬件电路结构图

1.1模拟信号垂直通道设计

模拟信号垂直调理电路允许输入的模拟电平范围在0~±25 V之间,输入阻抗可在1 MΩ与50 Ω之间切换,同时具备DC/AC/GND三种耦合方式。

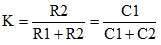

由于允许输入的模拟电平范围较大,而ADC允许输入电平范围较小,所以必须先对输入信号进行衰减,然后根据需要进行放大,使当前输入信号的峰值接近或者等于ADC的最大量程。因此,就要求前端衰减电路的输入阻抗要高,同时在板卡的整个通频带内的衰减分压比不变。要实现这样的要求仅简单地采用电阻分压是达不到目的。因为在下一级的输入以及PCB走线中均存在分布电容,这个分布电容的存在对被测信号的高频分量有严重的衰减,造成信号的高频分量的失真(脉冲上升时间变慢)。为此必须采用如图2所示的阻容补偿式分压电路,图中R1、R2为分压电阻(R2包括下一级的输入电阻),C1、C2为补偿电容(C2包括下一级的输入电容)。调节C2,当满足 时,分压比K在整个通频带内是均匀的,它被表示为

时,分压比K在整个通频带内是均匀的,它被表示为 ,这样的分压电路做成的衰减器就可以无畸变地传输窄脉冲信号,仅仅是信号幅度变为原来的1/K。

,这样的分压电路做成的衰减器就可以无畸变地传输窄脉冲信号,仅仅是信号幅度变为原来的1/K。

图2阻容分压电路图

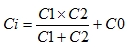

大多数数据采集设备的输入电阻Ri都设计在1MΩ左右,它的大小主要决定于R1,因为 ,而R1远大于R2。输入电容Ci为C1和C2的串联值和引线的分布电容C0的并联值

,而R1远大于R2。输入电容Ci为C1和C2的串联值和引线的分布电容C0的并联值 。本板卡的输入电阻Ri=1MΩ,输入电容Ci=25 pF。

。本板卡的输入电阻Ri=1MΩ,输入电容Ci=25 pF。

为了使探头接入被测电路不影响被测电路的工作,即前端衰减电路到下一级的可变增益放大电路应当是开路的,这可以通过加入一个输入阻抗很大的射随运放来实现,这里选用ADI公司的AD8027,其输入阻抗高达6 MΩ。

对衰减后的信号进行放大有三种方式:

1) 使用高精度运放,通过继电器或者模拟开关选择反馈电阻或者输入电阻的大小来实现不同的增益,缺点是需要较大的布线空间,不利于小型化,且高精度运放的输入带宽往往较窄,减小系统的重用性;

2) 使用数控可变增益放大器,这种方式利于控制且精度较高,缺点是增益的范围是不连续的;

3) 使用压控可变增益放大器,这种方式优点在于增益的范围是连续,缺点是要额外增加一个高精度DAC。

综合各方面的考虑,最终选用ADI公司的压控可变增益放大器AD8336及搭配TI公司的16位DAC DAC8552。

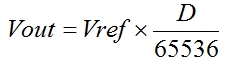

TI公司的DAC8552输出公式(1):

(1)

(1)

D范围为0~65536,Vref根据需要外接基准,但不能超出DAC电源电压。

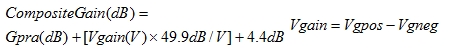

AD8336的增益分为固定增益和压控增益两个部分,其中固定增益根据带宽的选择已经精密电阻外接配置成4倍,则其总的增益为:

(2)

(2)

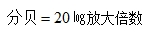

Gpra即为固定增益,单位为分贝(dB)。分贝与放大倍数的增益换算关系如下:

(3)

(3)

Vgpos与Vgneg由DAC8552输出得到,所以仅需根据选择的ADC的量程,算出对当前信号的增益需要,从而推导出DAC两端所需输出的电平大小,利用FPGA或者其它处理器控制即可。

最后还需把单端信号转成差分信号,原因有三:

1) 对ADC来说,差分输入信号采样精度更高;

2) 提高抗干扰能力;

3) 利于阻抗匹配。

1.2 数据采集及主控电路

选择高精度的ADC是构成一个优秀的测量系统的三个要素之一。衡量一个测试量与实际理想值的误差时,需要两个量来表述: accuracy 和 precision。前者一般称为精度,后者最好叫做可重复性。

Accuracy实际是测量中一个平均过程的概念。一般是衡量多次测量后的平均值接近理想值的程度。所以它隐含的是测试的DC量纲。在ADC的数据手册中的以下参量是一个DC的概念:Offset, gain error, INL, DNL等。它们衡量了做直流参量测量时的误差水平。

Precision是指在同样测试条件下,测试结果的一致性。同样的A/D系统中,以下参量是一个AC的概念:Dynamic Range, SNR, TDH等。它们衡量了做非直流参量测量时的误差水平。

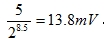

所以对ADC的选型并不是10位分辨率的性能就一定优于8位的分辨率的性能,更不是说对一个10位的AD系统输入5 V信号,其误差就在 。实际上ADC的精度其主要决定于两个参数:INL和ENOB。

。实际上ADC的精度其主要决定于两个参数:INL和ENOB。

INL是直流测量时要主要考虑的参数。一般ADC的其它直流测量误差诸如offset,gain error等可以通过校准而削掉。这时INL成了影响测试的主要误差来源。比如一个10 bit的ADC,INL=1.5 bit,则整个ADC的实际可得到的最好精度是 。

。

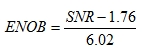

ENOB是非DC信号模数转换或交流测试时一个A/D的有效bit数。它主要跟SNR有关。其存在下列的公式:

(4)

(4)

其中的SNR更精确的说应该是SINAD(SNR & THD:信噪比和总谐波失真)。上边公式也隐含了如果系统的SNR变差,则总的测量precision也会变差。

经过对比对ADI、MAXIM、TI等公司的ADC,最终选择了ADI公司的AD9238,其INL仅为0.7 LSB,SNR达到70 dB。

ADC采集到数据通过数据总线传输给处理器。处理器方面,由于还涉及到CAN、RS485、PCI接口的设计,因此市面上并没通用的处理器提供。欧比特公司作为一家专注工控航空航天的公司,依托基于SPARC架构的IC设计,对FPGA的应用已十分成熟。针对成本、系统频率、资源及IO管脚的需求,最终选用了Altera公司的EP3C40作为处理器的IP核载体。

1.3 本地缓存及PCI接口电路

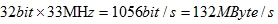

如前所述,国内工控方面的不间断数据采集研究,一直受限于PCI带宽。虽然PCI总线理论传输速率可高达 ,但这仅仅是理论值。实际上的PCI总线开发,能达到40 MByte/s的传输速率已经是相当不错的数据。欧比特公司在S698处理器、EMBC1000系列等产品的研发过程中积累相当丰富的PCI总线开发经验。经过努力,基于PLX公司的PCI9056可实现60 Mbyte/s的PCI传输速率,传输数据稳定有效、不丢数。

,但这仅仅是理论值。实际上的PCI总线开发,能达到40 MByte/s的传输速率已经是相当不错的数据。欧比特公司在S698处理器、EMBC1000系列等产品的研发过程中积累相当丰富的PCI总线开发经验。经过努力,基于PLX公司的PCI9056可实现60 Mbyte/s的PCI传输速率,传输数据稳定有效、不丢数。

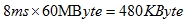

根据木桶理论,PCI总线的实际传输效率是一块短板,在这短板得以加长后,研发的难度就集中在另外一块短板——上位机取数上。也就是说即使PCI总线真的能够传输很快,但是上位机是否能都把数据读到?由于EMBC2000-PCI板卡是基于WinXP/Win2000操作系统的,有过PCI总线开发经验的人都知道,在大规模的连续数据传输中是不适宜使用中断方式的,因为这很容易导致CPU占用率过高,而导致系统进入假死状态。而使用查询方式,与即时的Linux系统不同,Windows操作系统是个分时操作系统,也就是说它的线程占用的时间是个不确定的值,就算单独为读操作开一个线程,但是也必须使数据在板卡缓存一端时间后,再由上位机查询到满状态后读走。但上位机读数据的过程中,A/D系统仍在不间断地采集数据,由于操作系统中没有一个线程能一直独占CPU。也就是说上位机并不能查询到一次满后,就一直在读数,每次读操作中必然存在一个间隔,也就是说PCI总线的传输速率需高于或者至少不低于采样速率。那么在这个间隔中,采集数据同样需要缓存在板卡的本地缓存中。

通过对WinXP系统的深入分析及驱动开发,最终确定需在板卡上缓存8 ms的采集数据,并在每个通道的缓存数据处理上采用“乒乓模式”,也就是说FPGA将ADC采集的数据轮流填到每个通道对应的缓存A与缓存B内,而当缓存A第一次满后,上位机开始查询读操作,轮流读走缓存A与缓存B的数据。依上,则所需要单个缓存的容量大小为 。另外考虑到选择如SDRAM、DDR-SDRAM、DDR2-SDRAM、SRAM布线复杂,且需要FPGA提供过多的IO及资源。由于一方面这会增加PCB的层数;另一方面只有高端的FPGA才会具备使用上述的缓存所需的IO口数量,而高端FPGA的价格通常是低成本FPGA价格的是十倍甚至更多。出于成本的考虑,选择了IDT公司的双口SRAM IDT70V659作为外部缓存,其容量达到512 KByte,速率达100 MByte/s,满足系统设计的需求。

。另外考虑到选择如SDRAM、DDR-SDRAM、DDR2-SDRAM、SRAM布线复杂,且需要FPGA提供过多的IO及资源。由于一方面这会增加PCB的层数;另一方面只有高端的FPGA才会具备使用上述的缓存所需的IO口数量,而高端FPGA的价格通常是低成本FPGA价格的是十倍甚至更多。出于成本的考虑,选择了IDT公司的双口SRAM IDT70V659作为外部缓存,其容量达到512 KByte,速率达100 MByte/s,满足系统设计的需求。

1.4 隔离型CAN/RS485接口电路

考虑到工控场合通常存在浪涌电压,EMBC2000-PCI板卡的CAN和RS485做了隔离处理,可防浪涌电压达1000 V,并针对RS485常出现的由于第三态存在而导致接收端输出处于不定态做了相应处理。

CAN逻辑方面,由FPGA搭载欧比特公司自研的OBT-CAN软核,支持BasicCAN和PeliCAN模式。在PeliCAN模式下,支持CAN2.0B的扩展特征。并具备1 KByte本地缓存,通讯速率最高达1 MByte。寄存器、性能方面完全兼容PHILIPS公司的SJA1000。

RS485逻辑方面,采用UART16550软核,并具备了64 Byte本地缓存,通讯速率最高达115200 bps,最大传输距离约为1200米。

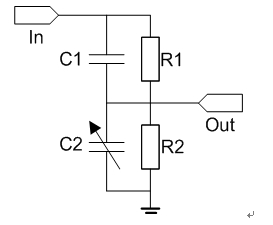

3 EMBC2000-PCI-AD485CAN的硬件逻辑

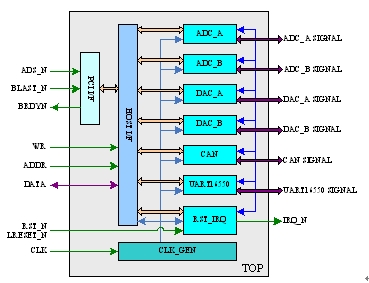

EMBC2000-PCI的硬件逻辑设计分成8个部分:ADC模块、DAC模块、CAN模块、UART16550模块、HOST I/F模块、PCI I/F模块、RST-IRQ模块、CLK_GEN模块。其中ADC模块及DAC模块是用于控制模拟信号垂直调理通道及对采集数据进行处理,两个通道的模块完全相同,仅需在顶层文件上进行复用即可。具体逻辑框图如图3。

图3 EMBC2000-PCI硬件逻辑框图

ADC模块负责控制ADC并对ADC的采集数据进行相关处理。为了降低成本,EMBC2000-PCI并没有设计专门的触发电路,而是在FPGA内部实现触发。该部分逻辑集成在ADC模块中。通过用户预设的边沿触发方式及触发电平,FPGA对采集数据寻找满足触发电平的对应点,然后再结合该点前后的数据进行趋向分析,判断是否是所需的上升沿或下降沿触发。当找到触发点后,FPGA才把采集数据按照用户预设的触发深度把数据存至本地缓存中。

DAC模块负责通过控制DAC从而控制可变增益放大器;CAN模块/UART16550模块分别实现了CAN2.0B协议、RS485通讯;RST-IRQ模块用于产生各种PCI中断信号;CLK_GEN模块用于进行锁相环倍频及产生全局同步时钟。

如前所述,由于采集数据是先存至本地缓存,然后由上位机直接读走,不再经过FPGA。所以FPGA与PCI桥PCI9056之间是一个异步系统,因此PCI接口与其它模块并需通过一个缓冲来实现同步。PCI I/F模块用于实现与PCI桥之间的通讯,而HOST I/F模块用于实现PCI通讯与内部其它逻辑之间的同步。

整个IP核运行速率为120 MHz,完整实现了板卡各类逻辑。

4软件设计

EMB2000-PCI的驱动基于Jungo公司的WinDriver开发,在上层软件运用如SinC/C插值法、交替描点法等算法实现波形的还原、描绘、计算,并可把波形进行实时游标测量、打印。EMBC2000-PCI通过DLL文件提供接口函数供二次开发。

5 结论

EMBC2000-PCI多功能数据处理板卡采用双数据存储方式、内部软触发方式实现了高达单通道20Msps/双通道10Msps的不间断数据采集能力,分辨率高12bit。板卡上的阻抗匹配与控制保证了数据采集的信号完整性。在数据采集方面已接近国际代表厂商美国Measurement Computing公司最高端产品PCI-DAS4020/12型板卡。CAN、RS485接口使数据可以进行远距离传输。EMBC2000-PCI的出现,较好地填补了国内在基于PCI总线的不间断数据采集方面的空白。

参考文献:

[1]PCI-DAS4020-12-UG.Measurement Computing,2009.

[2]PCI_9056BA_Data_Book_v1.3.PLX,2009.

[3]EMBC2000-PCI-AD485CAN用户手册 . 珠海欧比特控制工程股份有限公司,2010.

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码