高性能ZVS降压稳压器消除在宽输入范围负载点应用中提高功率吞吐量的障碍

作者/C.R.Swartz Vicor 公司 Picor 半导体解决方案首席工程师

当前具有更高整体效率的电子系统需要更高的功率密度,这为非隔离负载点稳压器(niPOL) 带来了大量变革。为了提高整体系统效率,设计人员选择避免多级转换,以获得他们所需要的稳压负载点电压。这就意味着niPOL需要支持更高的工作输入电压,提供更高的转换率。除此之外,niPOL还需要在保持最高效率的同时,继续缩小电源解决方案的总体尺寸。而且随着产品性能的提升,niPOL的功率需求会进一步提高。

电源行业通过对niPOL进行多项技术升级来应对这一挑战。过去几年,行业已经看到器件封装、半导体集成和MOSFET技术的显著进步,这带来了高度集成的紧凑解决方案。虽然这些解决方案在有限的电压范围内工作良好,但在10:1或12:1的适度降压比例下,效率与功率输出会略有下降,而在宽或超宽输入范围内、在降比接近36:1的情况下,其性能会大幅下降。

在过去几年对niPOL的各种改变中,对电源链拓扑本身的改变最少。显然,我们不仅看到了电流模式控制、仿真电流模式控制和数字控制等各种控制拓扑,而且还看到了同步整流和自适应驱动器等功率级的改进。这些技术带来了持续的改进和/或额外的设计复杂性。

硬开关降压稳压器拓扑本身极大地制约了宽动态工作范围内功率密度的改进。为了缩小电源系统的尺寸,您必须缩小其重要元件的尺寸。实现这一目标的最佳途径就是提高开关频率,但这有难度。在使用硬开关技术的情况下提高开关频率,就像增大漏水大坝的规模一样。这其中有3项根本性的挑战:

1.硬开关:由于高电压加在主高侧开关上,瞬间流过大电流所产生的与工作频率以及工作电压相关的开关损耗是宽动态范围内工作的直接障碍。具有更优异开关速率品质因数(FOM)的新一代 MOSFET 技术应支持更快开关。快速开关有着其自己的问题;硬开关(甚至快速开关)往往会带来开关节点的尖峰及振铃以及必须解决的 EMI 和栅极驱动器的可靠性问题。这些问题在更高电压及频率下会被放大,使得更快开关技术在需要更高电压或频率的更宽工作范围内优势大减。

2.体二极管传导:同步开关体二极管传导不利于高效率,会限制开关频率的最高水平。在高侧开关开启前和同步 MOSFET 关断后,同步开关体二极管一般具有一些传导时间。

3.栅极驱动损耗:在高频率下开关 MOSFET,会导致更高的栅极驱动损耗。

1仿真模型

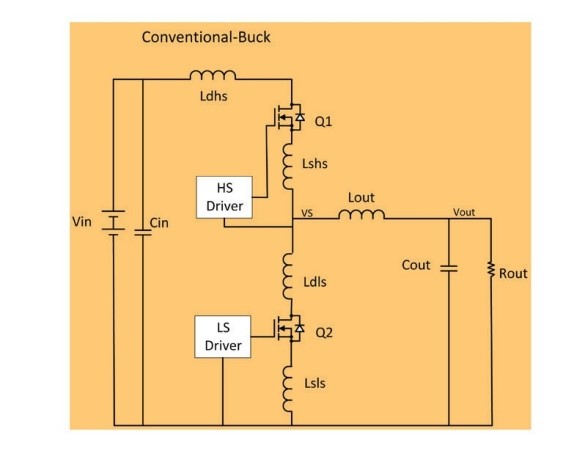

图 1 是典型常规降压拓扑的示意图以及相关寄生电感。这些电感可能存在于MOSFET寄生电感和/或PCB线迹本身的集总寄生电感中。为了以图形方式显示该拓扑在较高频率应用中使用时的制约因数,使用业界最佳的MOSFET(以及制造商的SPICE模型)构建仿真模型。

图 1常规降压拓扑

假定转换器设计工作输入电压为36 V,并在8 A满负载电流下降压至12 V。仿真分别使用2 µH电感和1 µH电感在650 kHz和1.3MHz下运行。MOSFEET的导通电阻为10 mohm。4个寄生电感针对Lsh设置为300 pH,而针对其它电感值则设置为100pH。寄生值主要根据与电源系统级封装(PSiP)电源设计概念有关的可用封装技术及布局方法确定。栅极驱动器使用4 ohm源极电阻最小化响声,使用1 ohm汲极电阻为高侧驱动器实现更快的关闭,而在这两种情况下,则为低侧驱动器使用1 ohm源极及汲极电阻。

2硬开关

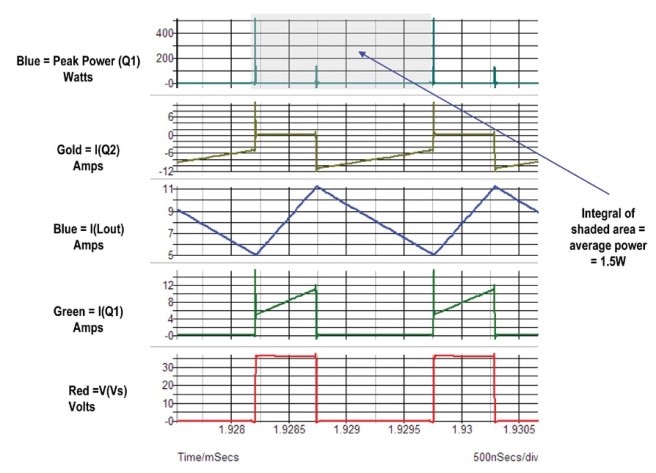

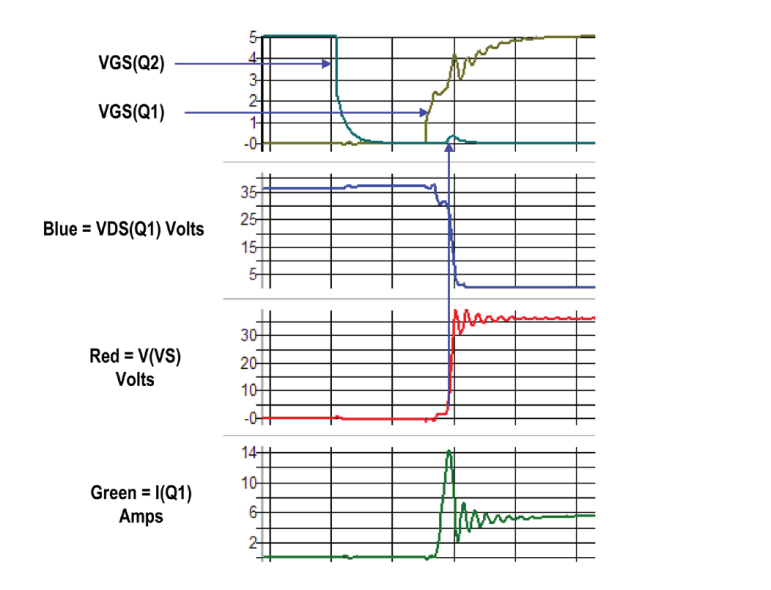

图2是高侧MOSFET Q1相对于VS节点电压及电流波形(Q1(绿色)、Q2(红色)和输出电感 Lout(蓝色))的瞬态功耗的仿真结果。

图2 650 kHz仿真(500 ns/div)

仿真结果说明开启损耗极高,关断损耗相对较低。两者之间是MOSFET RDS(on)主导的损耗,非常低。过去几年,MOSFET RDS(on)得到了显著改善。在大部分当前设计中,传导损耗很低,更容易管理。在整个开关周期综合瞬态功耗时发现,高侧MOSFEET在650kHz下的平均功耗为1.5 W,其中 0.24 W为传导损耗、0.213 W为关断损耗、1.047 W为开启损耗。总损耗的主要来源是Q1开启损耗。

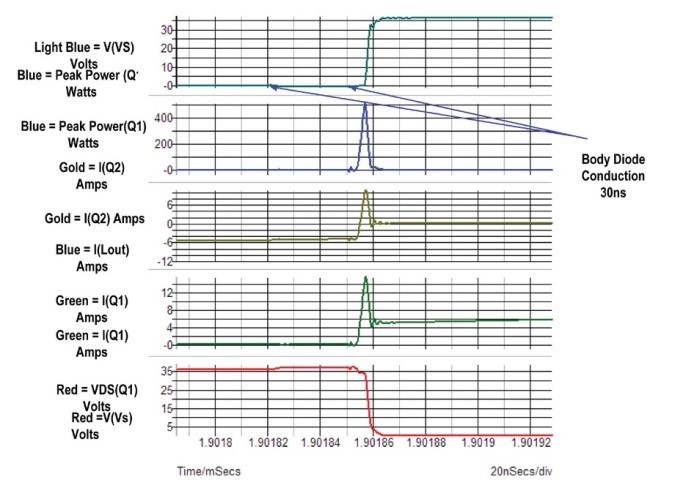

图3是高侧MOSFET Q1开启(包括开启前沿部分)前的快照。低侧MOSFET Q2的关断和Q1的开启之间有30 ns的死区时间。这一死区时间的作用是确保开启时不会发生MOSFET的交叉传导。因此,体二极管必须必须在死区时间内向电感续流。Q2的体二极管这段时间为正向偏置,电荷贮存在二极管的PN结中。在二极管能阻止反向电压之前,必须清空该电荷。这个过程被称为反向恢复。

在图3中,Q1的漏-源电压极高,接近VIN(受布局的寄生电感影响),同时也有极大电流流入Q2的体二极管。Q1必须消耗Q2体二极管的反向恢复电荷,同时还暴露在几乎全部输入电压下,因此峰值功率极大。高侧MOSFET源极电感Lsh对这一状况帮助不大。开启时,因其间的反向恢复电流压降,该电感会从MOSFET带走栅极驱动。该压降处于错误的方向,使得源电压相对于栅极电压有所上升,而此时驱动器正在努力克服开启的米勒效应。这会导致在米勒区更长的时间周期以及高侧MOSFET及驱动器更高的功耗。因此,在Q2体二极管恢复并能阻止电压之前,高侧MOSFET无法进入低电阻区。在峰值恢复电流达到其最大值后的复合时间内,Q2的体二极管同时承受着反向电流及反向电压,因此其中会有功耗。在复合完成后,体二级管中就没有功耗了。

图3 650 kHz仿真20 ns/div反向恢复效果

加速栅极驱动可轻微降低高侧MOSFET中的功耗。不过加速栅极驱动,Q1会以更快速度通过线性区,这会通过注入更大反向恢复电流,让Q2的体二极管更快反向恢复。由于寄生电感中贮存有能量,这会使VS节点更快上升。图4是我们650kHz仿真的栅极驱动以及Lsh从200 pH增大到500 pH对Q1驱动的影响。(注意:在 VS 上升的过程中,Q2 上会出现凸块。)因Q2的米勒电容和VS节点的dv/dt问题,该凸块会Q2的栅极驱动器耦合。不难想象加速Q1驱动的影响。更快的dv/dt不仅会在Q2的栅极上造成更大凸块,而且还会带来更大的响声。如果Q2是支持低栅极阈值的低压器件,Q2可能回导通,导致周期性交叉传导。这一交叉传导可能具有破坏性,也可能没有,但肯定会降低效率。此外,寄生电感中贮存的较大能量还可能会导致MOSFET上的电压过高,甚至可能需要掐断耗散。

图4 将Lsh提升至500 pH,对650 kHz仿真20 ns/div栅极驱动的影响

3更高频的工作

接下来使用较小的输出电感器,在两倍开关频率下再度运行常规降压仿真模型,以维持基本不变的峰值电流。对模型不做其它修改。1.3 MHz时,高侧MOSFET的总仿真损耗增大至2.73 W。

与650 kHz仿真相比,开关损耗均提高1倍。Q1中的RMS开关电流保持不变,因此传导损耗没有发生很大的变化。

如果只考虑Q1中的损耗,开关频率提高1倍会导致至少1.2%的效率降低。如果转换比例更大,对效率的影响还会大幅增加。这些结果说明,这并不是缩小尺寸、提高功率的最好方法。要缩小电源解决方案的尺寸并仍然提供有意义的输出功率能力,必须解决开关损耗问题,实现更高的开关频率。

4 ZVS 拓扑

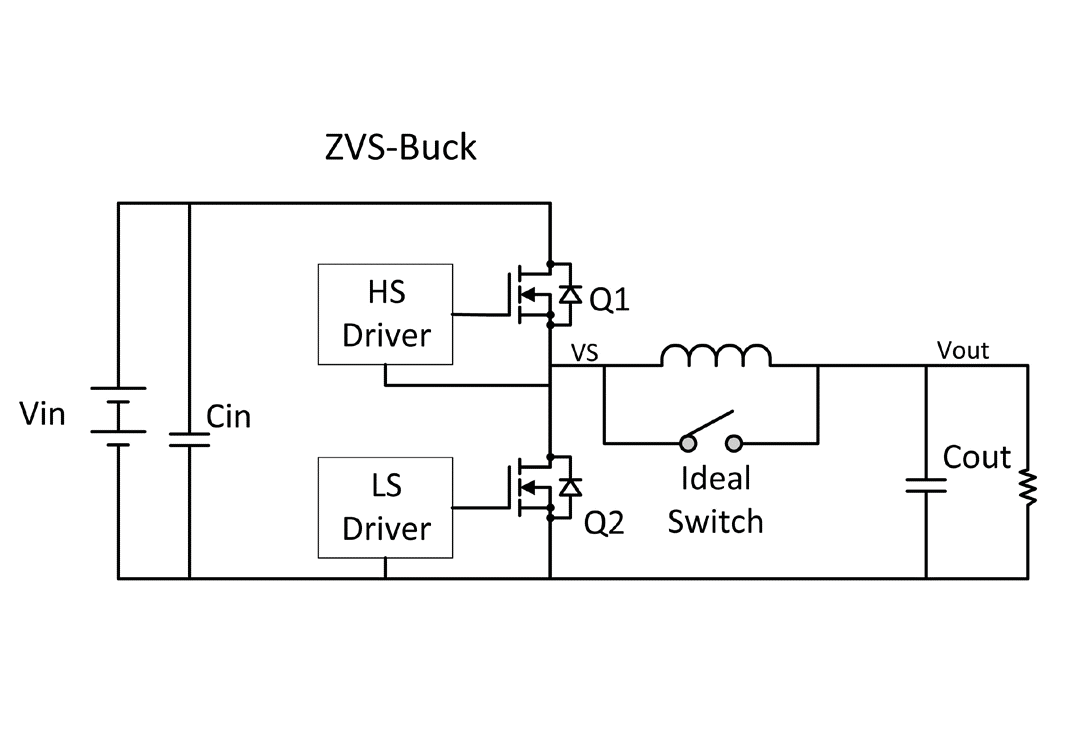

图5是ZVS降压拓扑的原理图。从原理图上看,除了在输出电感器上跨接一个额外的钳位开关外,它与常规降压稳压器完全相同。增加钳位开关的目的是让输出电感器中贮存的能量能够用于执行零电压开关。

图5 ZVS降压拓扑

图6 ZVS降压时序示意图

ZVS降压拓扑基本有三大状态,它们被定义为Q1导通阶段、Q2导通阶段和钳位阶段。要了解零电压开关的工作原理,您必须假定在谐振过渡后Q1在近乎零电压下开启。在D-S电压接近零时,Q1在零电流下开启。MOSFET和输出电感器中的电流会慢慢升高,直至由Q1导通时间、电感器间电压和电感器值共同决定的峰值电流。在Q1导通阶段,电能存储在输出电感器中,而电荷则提供给输出电容器。标黄的区域显示的是对应于Q1导通阶段的等效电路及电流。在Q1导通阶段,Q1的功耗由MOSFET导通电阻主导,开关损耗近可忽略。

接下来,在不足10 ns的极短体二极管导通时间后,Q1会迅速关断。该体二极管传导时间所增加的功耗可以忽略。在体二极管电流换向时,Q1会发生与峰值电感器电流成比例的关断损耗。接着Q2会开启,而且贮存在输出电感器中的能量会提供给负载和输出电容器。在电感器电流下降到零时,同步MOSFETQ2会保持导通,直至将一些能量存储在输出电容器的输出电感器中为止。这表现为电感器电流略变为负。Q2导通阶段及等效电路会出现在蓝色阴影区。

在控制器确定电感器中贮存有足够的能量后,同步MOSFET会关断,钳位开关会开启,从而会将VS节点钳至VOUT。钳位开关不仅可将输出电感器电流与输出隔离开来,同时还能够近乎无损耗地以电流方式循环贮存的能量。在钳位时间段里(极短),输出由输出电容器提供。

在钳位阶段结束时,钳位开关断开。输出电感器中存储的能量会与Q1及Q2输出电容的并行组合谐振,导致VS节点电压谐振到VIN的幅值。这种振铃会为Q1的寄生输出电容放电,减少Q2的寄生米勒电荷并为Q2的寄生输出电容充电。这允许Q1在VS节点接近VIN时,无损开启。包括谐振过渡和等效电路在内的钳位工作阶段显示为绿色区域。这里需要指出的是,当钳位开关导通时,电流按粉色电流环路循环;当钳位开关断开时,电流则按红色箭头流动。

这一拓扑采用多种重要方式解决了之前所述的局限性问题:

1.只要有钳位阶段,就没有在高侧MOSFET开启前需要高反向恢复电流的体二极管导通。

2.开启损耗基本完全消除。

3.高侧MOSFET栅极驱动不受寄生电感Lsh的影响。由于ZVS的作用以及无开启电流冲击,高侧MOSFET开启时消除了米勒效应。这有助于缩小高侧栅极驱动器的尺寸,并减少功耗。高侧MOSFET的开启速度不必特别快,可实现平稳的波形和更低的噪声。

5比较仿真

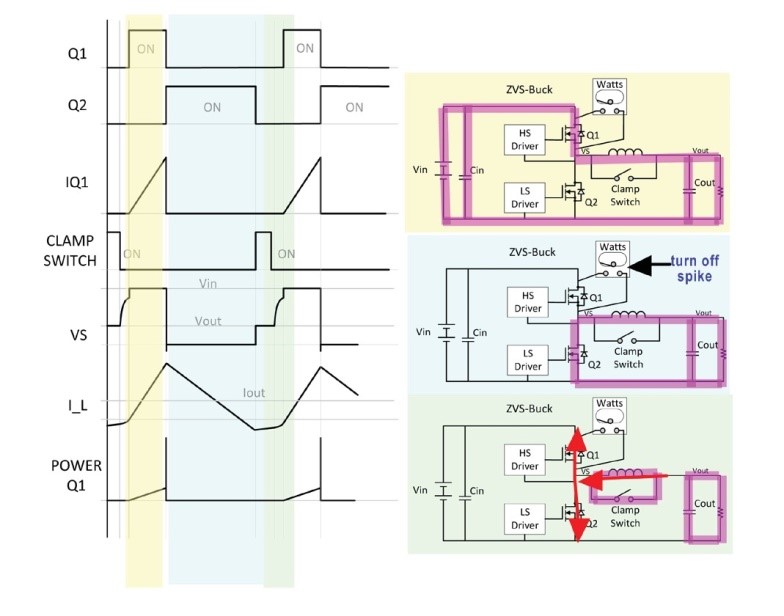

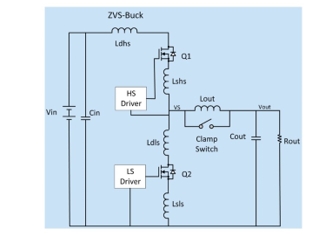

图7是使用之前寄生电感值的ZVS降压拓扑的原理图。仿真仍然运行相同的36 V至12 V稳压器(工作电流为8 A,频率为1.3 MHz),以便将高侧MOSFET的功耗与之前设计进行比较。ZVS降压使用230 nH电感器和与之前仿真相同的MOSFET及栅极驱动器特征。

图7带寄生电感的ZVS降压

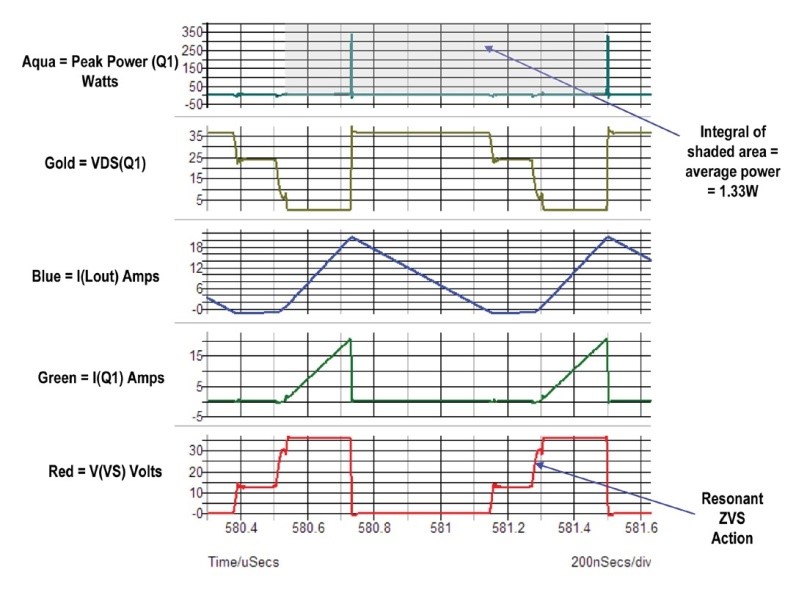

图8是工作频率为1.3 MHz的ZVS降压拓扑的仿真结果以及相对应的高侧MOSFETQ1的瞬态功率曲线。含开关损耗及传导损耗的平均功耗在高侧MOSFET中为1.33 W,甚至低于工作在一半开关频率下并使用较大电感器的常规稳压器。在两种设计都以1.3 MHz仿真时,高侧MOSFET的功耗降低更加明显,即1.37 W。从图8的功耗曲线可以看出,开启损耗近乎为零,开启时Q1中没有大电流尖峰。在Q1开启前没有体二极管传导,没有反向恢复效应,包括Q2体二极管中的反向恢复损耗。

该图是谐振过渡ZVS功能,包括MOSFET(Q1和Q2)输出电容(与Lout有响声)的并行组合。而且还可以看到,Q1的开启并非准确地发生在零电压位置上。使用Q1两端一些残余的电压开关它,一般可实现最佳整体效率,从而可减少钳位阶段需要循环的存储能量的数量。需要做出综合权衡,看是要最小化与钳位阶段有关的损耗,还是要通过在确切零电压下开关Q1来实现省电。栅极驱动器开启损耗还因去除ZVS功能所致的米勒电荷而降低。驱动器不必为Q1的G-D电容放电,因此高侧驱动器中的损耗会降低。此外,高侧驱动器不必在开启时与寄生电感Lsh对抗,因为该驱动器在开启时提供较少的电荷,而且Lsh中没有存储能源的大电流冲击。

图8 ZVS降压仿真波形

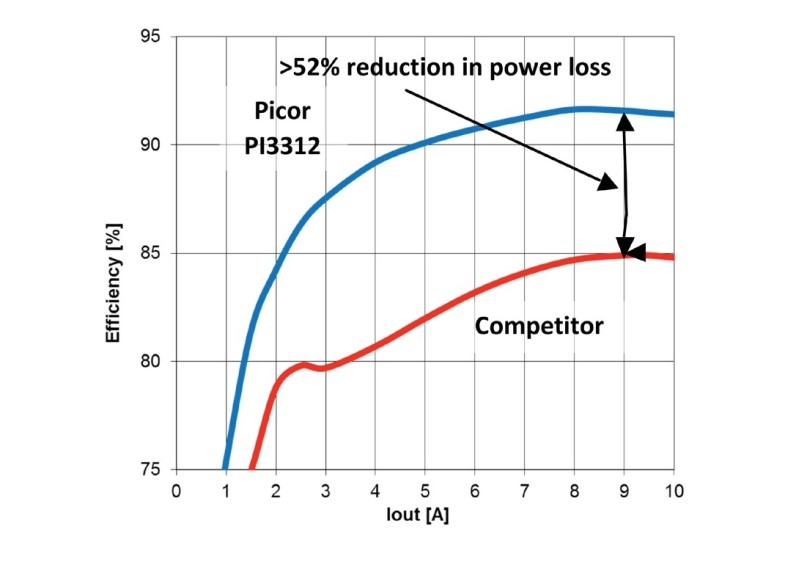

图9是在24VIN至2.5VOUT(9.6:1)10A设计中,电流同类竞争硬开关解决方案与ZVS降压拓扑之间的性能差异。满负载效率差异接近6.5%(轻负载效率也有明显差异),因此9 A测量点上功耗降幅超过52%。

图9 ZVS 降压 9.6:1步降24 V~2.5 V(10 A 时)性能与同类竞争解决方案的比较

6其它优势

基于ZVS降压拓扑与Picor的高性能硅芯片控制器架构的集成,开发出了PI33XX系列宽输入范围DC-DC稳压器。该DC-DC解决方案由10 mm x 14 mm SiP构成,包含只需外加一颗款输出电感器和几颗陶瓷电容器便能形成完整电源系统的所有电路。高开关频率允许使用极小的电感器。整个解决方案不仅尺寸(25 mm x 21.5 mm)小于同类竞争集成解决方案,同时还能以98%的峰值效率提供高达120 W的输出功率。PI33XX的最短导通时间是20 ns,从36 V输入向10 A负载点提供1 V输出,不仅效率超过86%,而且在从1 V到15 V的整个输出电压范围内,输出电流没有任何减少。

高级硅芯片与ZVS降压拓扑的完美结合,除带来宽输入范围和高效率外,还可带来一些其它优势。因为ZVS拓扑对控制增益斜率为-1、相移为90度的输出传输功能具有与生俱来的稳定性,在高频率开关的协助下,可实现带宽极大的反馈环路。PI33XX无需外部补偿(尽管可以添加一些)。闭环交叉频率一般为100 kHz,有55度相位裕度和20 dB的增益裕度。高闭环增益和小输出电感器允许闭环输出阻抗在宽频率范围内为低。这会导致极快的瞬态响应,在使用适度陶瓷输出电容值时恢复时间在20至30 µs之间,不需要其它大型存储电容器辅助。极为精确的输入前馈方法有助于误差放大器输出电压准确反映输出负载需求。这有助于执行极为简单的电流共享方法,通过并联Si增大输出功率。只需单独连接每个PI33XX误差放大器,便可准确并联均流。如果用户希望各个单元彼此追踪、一起同步,也可进行更多连接。

使用交错方式并联多达6个类似模型,既可同步PI33XX。PI33XX具有近乎理想的同步整流器驱动,允许高侧MOSFET关断与同步MOSFET开启间不到10纳秒的体二极管换向时间。这有助于降低高侧MOSFET的关断损耗和体二极管的传导损耗。除了高负载下的高效率优势外,PI33XX还使用极高效率的偏置系统和脉冲跳频模式,可实现优异的轻负载效率。见图9。

7灵活性

使用零电压开关的高性能硅芯片控制器架构能应用于升压拓扑及升降压拓扑等其它拓扑,只需重新排列电源开关,就能实现类似的优势。事实上,这将在高效率及更高输入电压下实现电源转换的任意组合,同时还可提供低开关损耗、高功率吞吐量并缩小解决方案尺寸。

8结论

ZVS降压拓扑可作为一种在不降低功率吞吐量的情况下缩小所需尺寸的方法。所介绍的名为PI33XX的新产品,不仅使用Picor高性能硅芯片控制器架构,而且还包含在高功率吞吐量和高效率下实现宽输入范围(8~36 V)至各项输出(1、2.5、3.3、5、12和15V等)所需的各种特性。另外,相同的高性能硅芯片控制器架构也能用于一般使用升压或升降压拓扑完成的硬开关应用,这可显著提高功率吞吐量和功率密度。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码