面向网络边缘应用的新一代神经网络

编者按: 介绍了面向网络边缘应用的新一代神经网络——微型二值神经网络,可在保持低功耗的同时减少对存储器的需求。

作者 / Hussein Osman

莱迪思半导体

Hussein Osman,在半导体行业拥有14年的经验,其中包括13年的系统设计工作经验,目前担任产品营销经理。在加入莱迪思之前,曾任赛普拉斯半导体公司的专家级系统工程师,致力于尖端的触摸、电容式触摸感应和指纹技术产品定义和开发。

人工智能(AI)、神经网络和机器学习领域的发展十分迅速,开发工程师正不断尝试为系统添加更多智能功能,前景不可估量。其中各类应用对于计算的需求是不同的。在数据中心领域,用于执行图像识别的神经网络是“经过训练”的,举个例子,通过向神经网络投喂成千上万的图像并分配权重直至神经网络能够正确识别对象。就像人类从一张白纸到最后成为知识渊博的人,当新数据出现时,人们能够根据过去的经验进行“推理”并做出决定,同样,系统必须使用“推理技术”根据神经网络从新数据上学到的东西来进行“推理”并得出结果。

建立数据架构并计算推理所需的权重可能需要数TB的数据和大量的计算资源。因此,数据中心常用的深度学习技术通常使用大尺寸、高性能GPU来满足如此大量的计算要求。

高功耗GPU对于想要将AI优势引入到网络边缘领域的设计工程师来说太过奢侈。在网络边缘领域,部署数据中心使用的基于浮点运算的深度学习技术是不太现实的。设计工程师必须开发计算效率高的解决方案,不仅要达到精度要求,还要满足消费电子市场对于设备的功耗、尺寸和成本的限制。尽管设备在数据中心接受过训练,可是一旦部署到网络边缘领域,就要尽可能使用更少位数进行计算来实现推理。为了简化计算流程,设计工程师从浮点数运算转为定点数运算,如果可能的话,甚至使用最基本的整数运算。通过改变训练的方式来补偿浮点数到定点整数的数据量级上的差异,设计工程师得以开发解决方案来实现更快的训练速度和更高的精度,从而将定点/低精度整数运算神经网络的性能提升至浮点数运算神经网络的水平。为了最为简单地构建的网络边缘设备,训练需要生成具有1位权重和激活的神经网络模型。这样的模型被称为二值神经网络。

VectorBlox Computing 和莱迪思半导体公司的工程师已经合作开发了一种新器件,以充分利用二值神经网络的优势。该器件通过二值方法优化了神经网络的尺寸、成本、功耗和性能,大大降低存储器需求,同时最大限度降低了功耗。这可以使用低功耗FPGA器件,例如iCE40 UltraPlus™来实现,该器件提供了具备充足存储器、逻辑和DSP资源的灵活平台。研究成果发表在第三届关于FPGA资源重新整合(Overlay Architectures for FPGA, OLAF)年度研讨会论文中。

开发团队将这个全新的概念称为微型二值神经网络(Tiny Binarized Neural Network)或TinBiNN。二值神经网络(BNN)无需乘法和除法运算,可降低对于存储器的要求,并且仅使用加法和减法来计算卷积。开发团队将TinBiNN定义为可使用少于5400个4输入查找表(LUT)资源实现的BiNN。本文讨论的重点是基于少于5000个4输入LUT的轻量级TinBiNN,以及如何使用莱迪思半导体的UltraPlus™FPGA实现。

1 二值神经网络

基于CNN的机器学习应用中,计算内核是一个卷积核,一个3×3窗口的权重与输入数据相乘,然后求和成一个纯量结果。输入值、权重和结果通常使用浮点数系统。虽然硬件优化支持窄定点值,但乘法仍占主导地位。

最新的理论,如M.Courbariaux,Y.Bengio和J.-P. David的“BinaryConnect: Training Deep Neural Networks with Binary Weights During Propagations”论文中使用二进制权重来表示+1或-1,消除了乘法运算[1]。该项目使用浮点数据在CIFAR 10图像识别数据集上实现了8.3%的误差率。

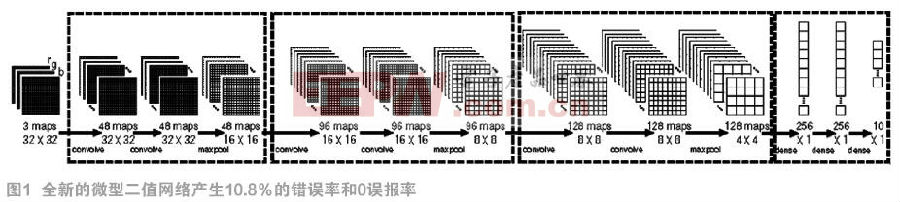

VectorBlox和莱迪思的开发工程师对BinaryConnect方法进行了三项改进。首先,他们把网络结构减小了一半。工程师们将(2x128 C3) – MP2 – (2x256C3) – MP2 (2 x 512C3) – MP2 – (2x1024FC) - 10SFC架构简化为(2 x 64C3) - MP2 – (2 x 128C3) - MP2 - (2 x 256C3) – MP2 – (2 x 256FC) - 10SFC,其中C3是3×3 ReLU卷积层,MP2是2×2 max-pooling层,而FC是一个完全互连层。

然后团队通过对所有输入数据使用8位有符号的定点数进一步优化网络。累加器使用32位有符号数来防止溢出,然后在数据传递到下一层之前通过饱和操作变成8位。新系统的错误率为10.8%。神经网络的规模缩小至48-48-96-96-128-128和64-128-10,错误率增加到11.5%。

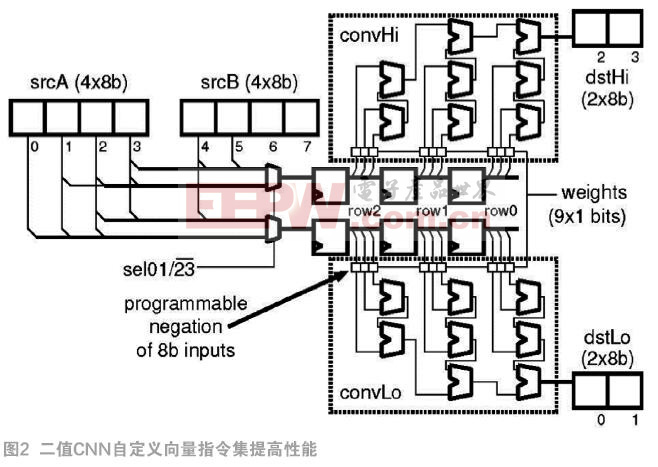

第二项改进是为二值神经网络实现硬件加速器。然后开发工程师使用加速器作为ORCA软RISC-V处理器中的ALU。RISC-V软处理器以其高效率的RV32IM指令集闻名,使得开发工程师能够以更少的资源进行更多的计算。在这种情况下,开发工程师使用一组自定义轻量矢量扩展(LVE)指令增强了ORCA处理器。通过RISC-V ALU传输矩阵数据,LVE减少或消除循环、存储器访问和地址生成开销,从而提高了矩阵运算的效率。将CNN加速器作为自定义矢量指令(CVI)(见图2)添加到LVE,进一步提升了运算效率。

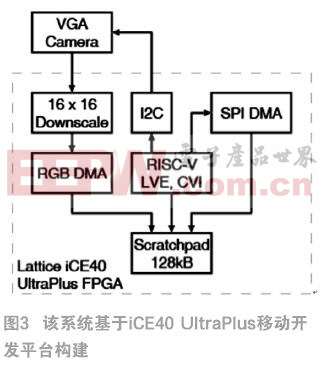

第三项修改是在iCE40 UltraPlus FPGA中实现了增强的RISC-V处理器。为了在网络边缘执行推理任务,设计工程师需要一种能够提供高度并行架构的解决方案,支持以低功耗每秒进行大量运算。对于希望通过语音或图像识别技术为网络边缘应用添加更多智能功能的设计工程师而言,iCE40 UltraPlus可提供连接图像传感器所需的灵活I/O以及丰富的逻辑资源,用于缩放和处理捕获的图像数据。iCE40 UltraPlus还具备8个DSP模块,支持更复杂的算法,而片上存储器则可以在低功耗状态下缓冲数据。LVE直接在128 kB暂存RAM上运行,该暂存器RAM已经三倍超频,可以在每个CPU时钟周期内进行两次读取和一次写入。二进制权重存储在内部RAM中,所以如果任何LVE操作正在进行,DMA引擎都可以将这些值高效地转移到暂存器中,不必占用CPU时钟周期。

开发工程师使用iCE40 UltraPlus移动开发平台,对FPGA器件的关键互连功能进行评估,快速实现原型设计和测试。概念验证演示可帮助工程师快速开发驱动和接口等解决方案。该平台可提供速率高达108 Mbps的1个MIPI DSI接口、4个麦克风桥接和多种传感器。在这个平台上,FPGA可以通过板载SPI闪存或USB端口进行编程。

开发团队采用Omnivision OVM7692 RGB摄像头(640 x 480像素),并使用RGB565在硬件层面将图像压缩至40 x 30像素。DMA用于将RGBA8888像素写入暂存器。软件对RGBA8888像素进行去交错,并将结果填充到尺寸为40 x 34的独立R8、G8和B8像素平面,其中只有32 x 32像素的数据是重要的。

开发工程师创建了一个人脸检测器,这是通过使用修改的CIFAR-10数据集对10类分类器进行训练,用CIFAR-100中“人”的重复图像替换“鹿”图像实现的。为了提高性能,团队进一步缩小网络结构,并使用175,000个面部和非面部图像的专用数据库来训练全新的1类分类器。这个数据库包括各种人脸图像,涵盖各个年龄、种族、是否戴眼镜、帽子和太阳眼镜等信息。

2 低错误率,低功耗

初步结果很不错。在开发平台上,10分类分类器运行时间为1315 ms。 这款小尺寸CPU的工作频率为24 MHz,并使用iCE40 UltraPlus 5K器件的5280个4输入LUT中的4895个。它还使用FPGA的8个16x16 DSP模块中的4个,30个4 kb(0.5 kB)BRAM中的26个以及全部4个32 kB SPRAM。ORCA RISC-V上的加速器将卷积层的运行效率提高了73倍,LVE将密集层的运行效率提高了8倍。最终的结果是整体速度提高了71倍。

1分类分类器运行时间为230 ms,误差为0.4%,功耗为21.8 mW。低功耗版本设计运行速率为1帧/秒,而功耗仅为4.4 mW。上述两个分类器的错误率主要归因于训练,而不是精度的降低。图像传感器的功耗不包括在该分析中,尽管低功耗图像传感器能够以1-2 mW的功耗实现上述帧速率。

3 潜在的应用

基于TinBiNN神经网络的小尺寸、低功耗解决方案可以在网络边缘领域实现各类应用。例如,智能门铃可以使用嵌入式AI功能自动进入待机模式,直到有人出现。智能电视机可在没有观众的情况下自动关闭。同样,智能安防摄像头可使用嵌入式人工智能功能来减少或避免错误报告,只有当入侵者出现时才发送警报,而不是在狗、猫或其他动物出现在摄像头面前时发出警报。

具备面部识别的移动设备和平板电脑需要用户在进行面部识别之前唤醒设备。该解决方案使得这些设备能够以低功耗持续侦测人脸,然后唤醒高功耗应用处理器执行深度识别任务。

4 结论

将AI引入网络边缘领域是挑战与机遇并存的。正如本项目所展示的,使用FPGA和RISC-V处理器代替基于云的资源来构建AI可以大幅降低功耗,同时缩短响应时间。同时,本地数据保存和处理提高了安全性,节省了宝贵的带宽。通过将AI集成到器件中,设计工程师即使在网络关闭以节省功耗的情况下也能实现实时工作的智能功能。

参考文献: [1]Courbariaux M,Bengio Y,David J P.BinaryConnect: Training Deep Neural Networks with Binary Weights during Propagations.Advances in Neural Information Processing Systems 28(NIPS 2015).Curran Associates,Inc.,2015:3123-3131

本文来源于《电子产品世界》2018年第1期第79页,欢迎您写论文时引用,并注明出处。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码