JLink和JTAG接口引脚定义和使用方法

JTAG各类接口针脚定义、含义

一、引脚定义

Test Clock Input (TCK) -----强制要求1

TCK在IEEE1149.1标准里是强制要求的。TCK为TAP的操作提供了一个独立的、基本的时钟信号,TAP的所有操作都是通过这个时钟信号来驱动的。

Test Mode SelecTIon Input (TMS) -----强制要求2

TMS信号在TCK的上升沿有效。TMS在IEEE1149.1标准里是强制要求的。TMS信号用来控制TAP状态机的转换。通过TMS信号,可以控制TAP在不同的状态间相互转换。

Test Data Input (TDI) -----强制要求3

TDI在IEEE1149.1标准里是强制要求的。TDI是数据输入的接口。所有要输入到特定寄存器的数据都是通过TDI接口一位一位串行输入的(由TCK驱动)。

Test Data Output (TDO) -----强制要求4

TDO在IEEE1149.1标准里是强制要求的。TDO是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过TDO接口一位一位串行输出的(由TCK驱动)。

Test Reset Input (TRST) ----可选项1

这个信号接口在IEEE 1149.1标准里是可选的,并不是强制要求的。TRST可以用来对TAPController进行复位(初始化)。因为通过TMS也可以对TAP Controll进行复位(初始化)。所以有四线JTAG与五线JTAG之分。

(VTREF) -----强制要求5

接口信号电平参考电压一般直接连接Vsupply。这个可以用来确定ARM的JTAG接口使用的逻辑电平(比如3.3V还是5.0V?)

Return Test Clock ( RTCK) ----可选项2

可选项,由目标端反馈给仿真器的时钟信号,用来同步TCK信号的产生,不使用时直接接地。

System Reset ( nSRST)----可选项3

可选项,与目标板上的系统复位信号相连,可以直接对目标系统复位。同时可以检测目标系统的复位情况,为了防止误触发应在目标端加上适当的上拉电阻。

说明:

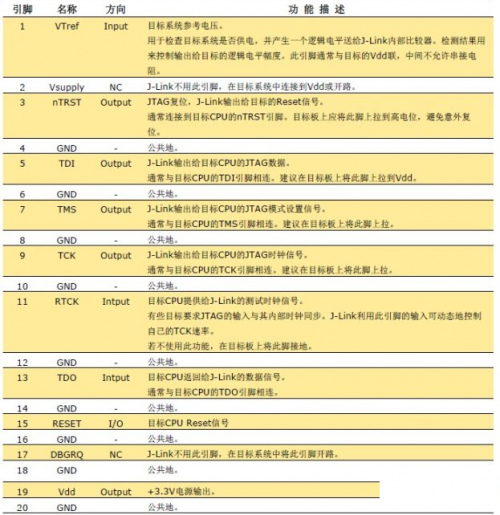

1脚:通常连接到目标板的vdd,用来检测目标系统是否供电;检测原理上图中有简单的说明。

2脚:原版的JLink这个引脚没有使用,不提供Vsupply输出,而很多改造版的JLink通过跳线选择从该引脚输出3.3V的电压给外边,我的就是这样的。

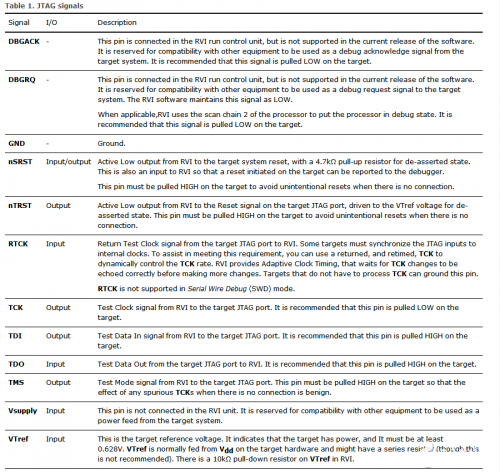

JTAG interface signals

The following table describes the signals on the JTAG interfaces:

ARM系统的JTAG接口的设计不当往往使硬件系统无法调试,所以在设计ARM系统前要先熟悉ARM系统的JTAG接口的定义和常见问题。

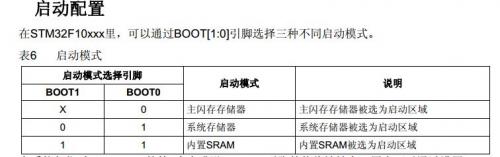

1.ARM系统的JTAG接口是如何定义的? 每个PIN又是如何连接的?

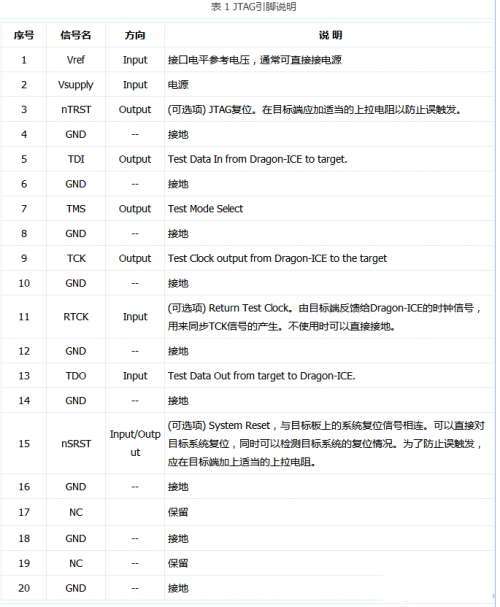

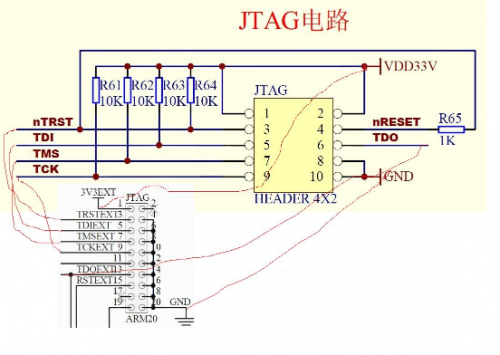

下图是JTAG接口的信号排列示意:

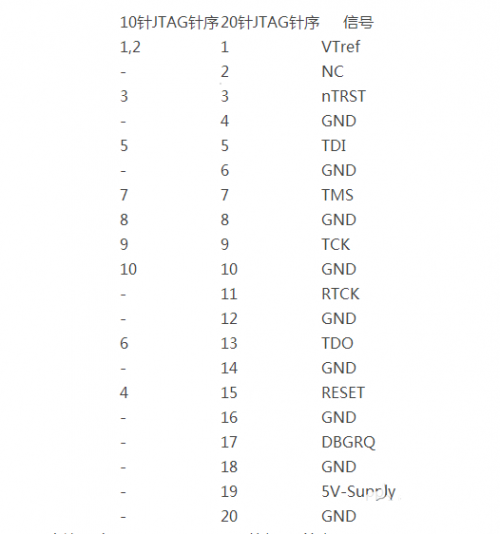

接口是一个20脚的IDC插座。下表给出了具体的信号说明:

目标系统如何设计?

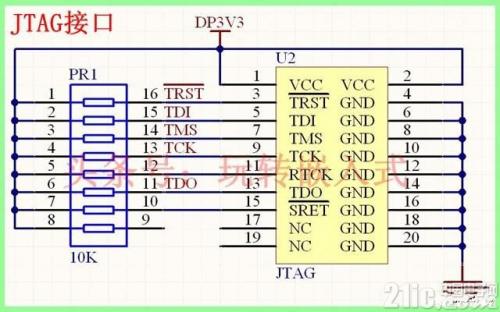

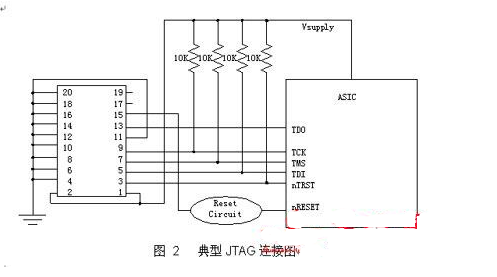

目标板使用与Dragon-ICE一样的20脚针座,信号排列见表1。RTCK和 nTRST这两个信号根据目标ASIC有否提供对应的引脚来选用。nSRST则根据目标系统的设计考虑来选择使用。下面是一个典型的连接关系图:

复位电路中可以根据不同的需要包含上电复位、手动复位等等功能。如果用户希望系统复位信号nSRST能同时触发JTAG口的复位信号nTRST,则可以使用一些简单的组合逻辑电路来达到要求。后面给出了一种电路方案的效果图。

在目标系统的PCB设计中,最好把JTAG接口放置得离目标ASIC近一些,如果这两者之间的连线过长,会影响JTAG口的通信速率。

另外电源的连线也需要加以额外考虑,因为Dragon-ICE要从目标板上吸取超过100mA的大电流。最好能有专门的敷铜层来供电,假如只能使用连线供电的话,最小线宽不应小于10mil (0.254mm)。

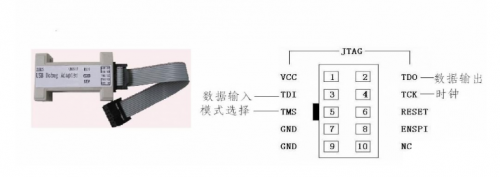

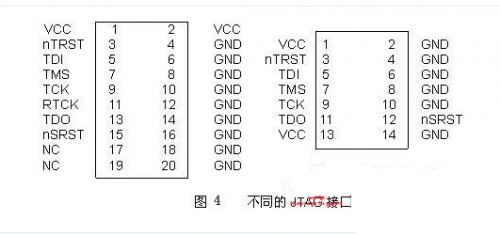

14脚JTAG如何与20JTAG连接?

Dragon-ICE使用工业标准的20脚JTAG插头,但是有些老的系统采用一种14脚的插座。这两类接口的信号排列如下:

这两类接口之间的信号电气特性都是一样的,因此可以把对应的信号直接连起来进行转接。Dragon-ICE配备这种转接卡,随机配备。

JLINK 10针J和20针JTAG接口连接方法

下面说一下接法,其实根本不需要什么转接板什么的,直接把相应的几根线对接就可以用了,所以要参考电路图,上面为TQ2440开发板的JTAG电路图,下面为JLINK的20针电路图,下面的JLINKV7电路图是标准接口,网上到处都能找到

实际上只需要接4跟线,4号是自连回路,不需要接,1,2接的都是1管脚,而8,10接的是GND,也可以不接。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码