高云半导体推出GW2A系列FPGA芯片的DDR类储存器接口解决方案

山东济南,2017年10月10日讯,山东高云半导体科技有限公司(以下简称“山东高云半导体”)今天宣布推出基于中密度晨熙Ⓡ家族的GW2A系列FPGA芯片的DDR类储存器接口IP核初级版(Gowin Memory Interface IP),包括相关IP软核、参考设计及开发板等完整解决方案。

高云DDR类储存器接口IP核初级版目前是一个通用的DDR2存储器接口IP,兼容JESD79-2标准。该IP包含通用的DDR2内存控制器(Memory Controller,MC)与对应的物理层接口(Physical Interface,PHY)。后续升级版会支持晨熙Ⓡ家族的GW2AR系列内嵌DDR类储存器式FPGA,功能升级将延及DDR1、DDR3内存控制器与对应的物理层接口。

高云DDR类储存器接口IP核初级版为用户提供一个通用的用户命令接口,另一端通过PHY连接至内存芯片,完成用户对存储器的访存要求。“高云DDR类储存器接口软核品种丰富,能支持目前市场上的主流DDR类储存器。”高云半导体软核研发部门负责人高级经理高彤军先生解释说,“目前推向市场的IP核初级版已经能够满足我们很多客户的应用要求,但是还远远没有达到高云器件的潜力,我们最终目标速度是达到800Mbps到1Gbps的范围。”

“我们提供简明易用的IP调用界面,同时提供可用于验证DDR2控制器IP性能的开发板和参考设计。”高云半导体市场副总裁兼中国区销售总监黄俊先生表示,“高云半导体会持续在IP核的开发方面加大投入,旨在提高用户FPGA的设计余量和整体系统的可靠性,同时缩短用户的设计周期,可以让广大用户尽快熟悉国产FPGA的架构,逐渐认同国产FPGA品牌的品质和良好的技术支持服务。”

IP主要特征

DDR2 MC与PHY的时钟比例为1:2;

支持存储器数据路径宽度为8、16、24、32、40、48、56、64和72位;

支持单列UDIMM和SODIMM内存模块;

支持x4、x8和x16两种数据宽度的内存芯片;

可编程突发长度4或8;

可配置的CL;

可配置的CWL;

可配置的tFAW;

可配置的tRAS;

可配置的tRCD;

可配置的tRFC;

可配置的tRRD;

可配置的tRTP;

可配置的tWTR;

支持动态片上终端ODT的控制;

支持自动刷新和用户启动刷新,自动刷新间隔可配置。

IP工作频率

l DDR2 SDRAM数据速率目前为500Mbps~560Mbps;

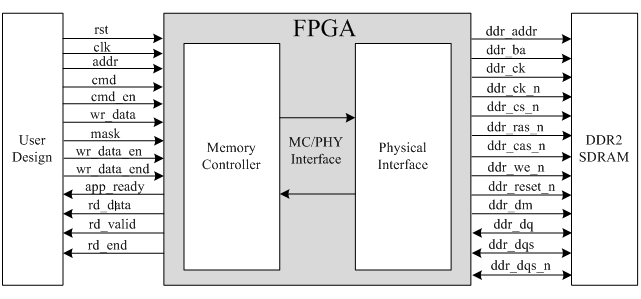

IP整体结构

高云DDR类储存器接口IP核的基本结构,包含Memory Controller、Physical Interface等主要模块。图中的User Design block 是FPGA中需要与外部DDR2 SDRAM芯片所连接的用户设计。

GW2AR、GW2A系列FPGA

GW2AR系列为内嵌DDR类储存器式FPGA,GW2A系列FPGA支持外挂DDR类储存器。其中,GW2AR-18K LQ176内嵌128M DDR1;GW2A-18KBGA封装与 GW2A-55K BGA封装支持外挂DDR2。

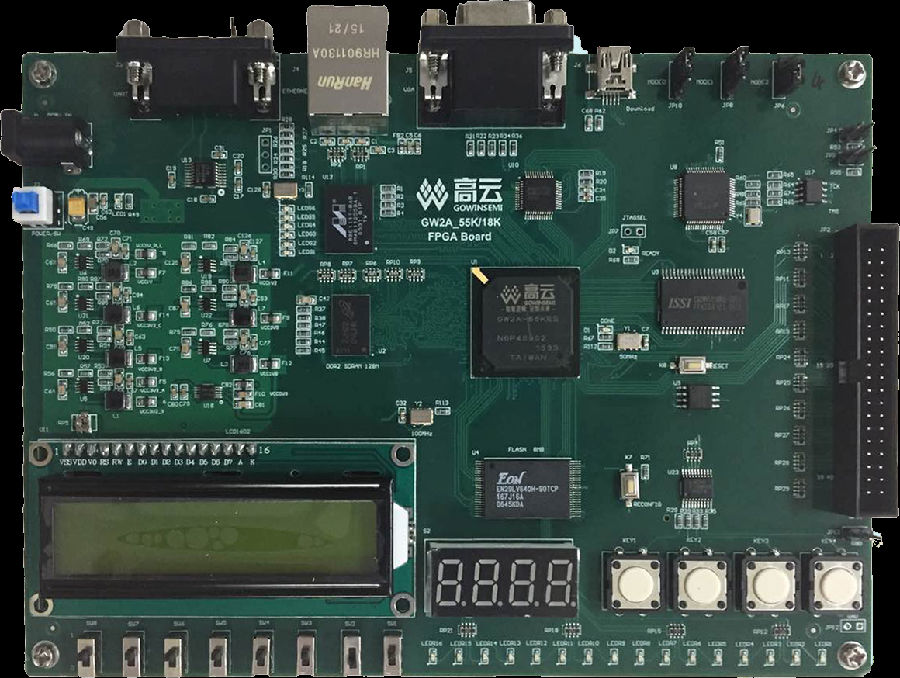

开发板与参考设计

高云DDR类储存器接口IP核初级版, 参考设计及开发板支持GW2A-18K/55K BGA封装FPGA对接通用DDR2存储器,后续升级版会支持GW2AR系列内嵌DDR类储存器式FPGA,功能升级将延及DDR1、DDR3内存控制器与对应的物理层接口。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码