AVR工具指南(二)

继续

3.

WinCUPL(可编程逻辑通用编译器)是一款可以为SPLD和CPLD创造出非常复杂的逻辑设计的逻辑编译器。该工具使得工程师们可以设计出他们自己的逻辑电路并创建出JEDEC(联合电子设备工程委员会标准)文件。因此,你可以使用ROM writer在设备中进行映射。

WinCUPL()

The WinCUPL 套件包含如下工具:

WinCUPL

CUPL Compiler

Simulator

WinSim

3.1.

1)

2)

图 3‑1. Atmel网站中下载WinCUPL的地址.

1)

2)

3)

4)

图 3‑2. WinCUPL’s 主界面.

3.2.

这一节介绍的是CUPL的设计操作,并向你展示了关于设计流程的样例。

3.2.1.

基本的逻辑和算数运算符,以及二进制等式设计中使用的函数如下。

1)

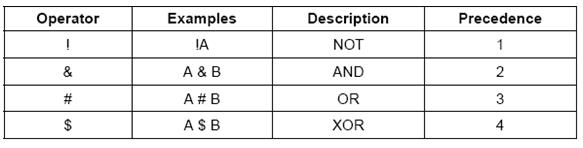

下表显示了使用NOT,AND,OR和XOR等逻辑运算符的表达方式和优先级。

2)

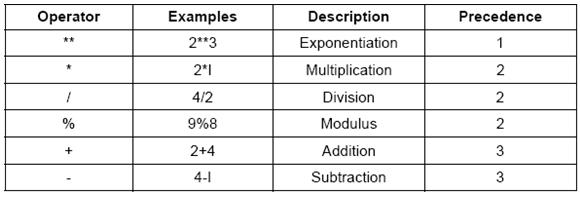

下表显示了6个常用的运算符的表达方式,样例以及优先级。

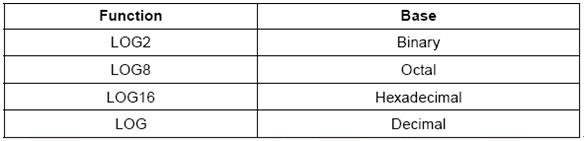

用$repeat和$macro指令定义的算数函数可以被用在算数表达式中。下表显示了算数函数和它的进制数。

3.2.1.

现在,我们开始介绍如何通过简单的样例来设计PLD。按照如下步骤,你可以执行包含等待功能的PLD。

关键词: AVR工具指

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码