ARM MPCore --(1)

1. Barriers and Synchronization

DSB -- Data Synchronization Barrier

DMB -- Data Memory Barrier

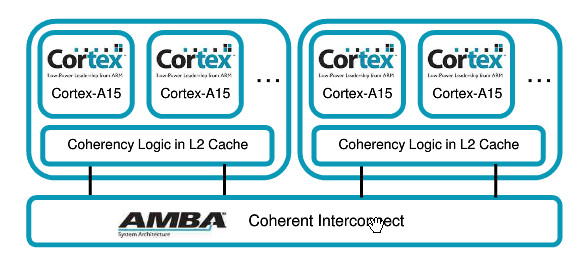

2. Cluster

Cortex-A15 MPCore,结合AMBA 4 ACE,支持多个coherent clusters.

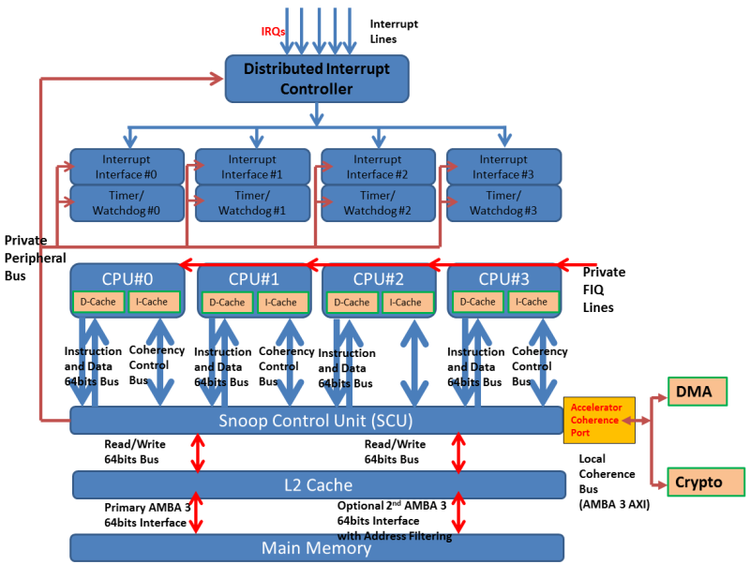

使用Snoop Control Unit同步每個Core各自的L1 Data Cache內容,並以Distributed Interrupt Controller支援既有的ARM Interrupts,每個處理器都有一個專屬的Timer與WatchDog,支援Level 2 AMBA(AXI high-speed Advanced Microprocessor Bus Architecture)介面,每個處理器都有一個Integral EmbeddedICE-RT Logic用以提供JTAG除錯介面,與各自的Pipeline,Branch Prediction with Return Stack,與CoProcessors 14 and 15,每個處理器都有自己的MMU (Instruction and Data Memory Management Units),主要的差異在於處理器對分頁的處理不是直接跟單核心架構一樣去操作TLB,而是每個處理器都維護自己的Micro TLB,並透過共用的Main TLB同步,每個處理器都有L1 Instruction/Data Cache,每個處理器都具備對外的32-bit Instruction Interface與64-bit Data Cache,每個處理器都支援硬體的Data Cache Coherence,每個處理器都可提供Vector Floating-Point (VFP) Coprocessor .

关键词: ARMMPCor

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码