基于USB3.0协议的PC与FPGA通信系统的设计

摘要 针对USB2.0在高速数据采集系统中带宽局限问题,设计了一款基于USB3.0总线的高速数据采集接口系统。通过对USB3.0的接口硬件系统、设备固件以及SLAVE FIFO与FPGA接口读写操作的设计,并经过实验测试,USB3.0硬件传输速度可达260 MByte·s-1,连续数据采集传输速率可达100 MByte·s-1且数据保持稳定。

随着USB3.0解决方案的出现,其在保留USB固有优势的基础上大幅提高了数据传输的带宽,适用于高速数据采集领域。本文针对基于USB的高速数据采集系统进行研究,设计了一款基于CYUSB3014芯片的USB3.0高速数据采集接口系统,该系统基于USB3.0协议来实现PC机与FPGA的数据传输。本文介绍了USB3.0固件的设计方法,GPIF II接口特性以及SIAVE FIFO与FPGA的读写操作设计。

1 USB3.0系统结构的设计

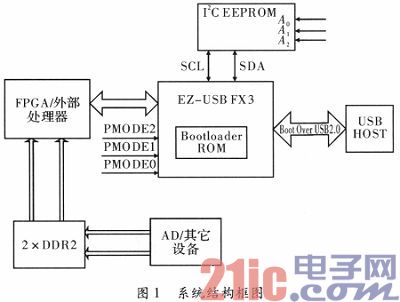

如图1所示,USB3.0系统的主芯片架构为Cypress公司FX3系列CYUSB3014 USB3.0控制芯片、FPGA芯片EP3CA0F484、DDR2芯片MT47H64M16HR。

CYUSB3014 USB专用控制芯片是新一代USB外设控制器,具有高度集成的灵活特性,可帮助开发人员为任何系统添加USB3.0功能。其拥有工作频率可达200 MHz的32 bit的ARM9内核,使得FX3能够应用在对数据处理要求较高的地方。芯片内部集成了一个512 KByte SRAM,用于存储代码、配置参数,同时用作芯片内部DMA通道的缓冲区。并集成了可编程的100 MHz的GPIF II接口能连接多种类型外部器件,支持最大32个可编程物理端点。

2 FX3固件的设计

固件是用以完成驱动程序无法完成的USB芯片及其外围芯片的初始化及控制工作的代码。FX3固件的主要功能包括:初始化参数的配置、辅助完成设备的重新枚举机制、对中断的处理、数据的接收与发送以及对外围的控制。FX3的固件设计只需调用相应的库函数,而不需要设计者过分关注底层硬件设置,大幅降低了固件的开发难度。EZ—USB FX3的固件设计主要包括对GPIF II接口、DMA通道及回调函数的设计。本文主要对GPIF II接口以及DMA通道加以介绍。

2.1 GPIF II接口

GPIF II接口是FX3与外部设备连接的重要组成部分,利用该接口可以实现与任何外部设备的高速并行数据传输。它具有一个提供多达256个可编程状态的完全可编程的状态机,可实现与任何处理器、ASIC、DSP或FPGA等的设备的无缝连接。GPIF II接口可在100 MHz的工作频率下实现32 bit数据的并行传输,最高有效数据的传输速率可达400 MByte ·s-1。该接口可配置为主机模式或从机模式,且数据总线可在8 bit、16 bit及32 bit之间灵活选择。

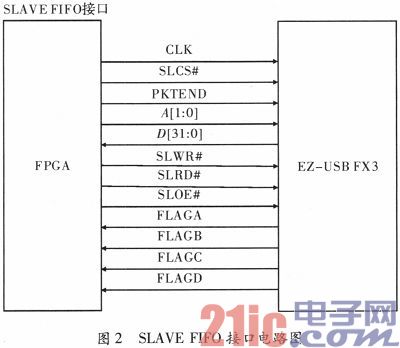

设计将GPIF II接口配置为32位同步SLAVEFIFO模式,外部处理器可像对普通FIFO一样对FX3FIFO进行读写。由PCLK信号作为接口状态机的工作时钟,接口上的地址信号A0:A1表示要访问的线程,FPGA通过检测4个标志信号FLAGA~D来检测缓冲FIFO是空或者满。配置为SLAVE FIFO模式的GPIF II与外部设备的信号连接如图2所示。

2.2 DMA通道

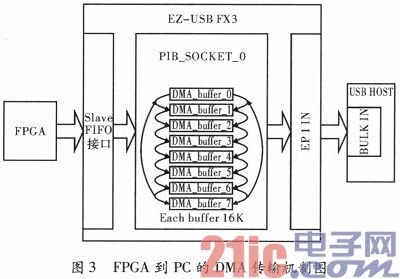

FX3内部通过DMA通道将不同外围接口连接起来,以实现不同接口之间的数据传输。DMA通道是一种软件结构,该结构封装了套接字、缓冲区和描述符3种硬件元素。套接字是存在于外部接口中的硬件模块,一个外部接口可以包含多个套接字,在固件系统中套接字处于DMA通道的两端,一个套接字用于输入数据,另一个则用于输出数据。数据通过套接字流入或流出已建立好的DMA数据通道。缓冲区是控制器系统内存中的数据缓冲区,相当于DMA数据通道中的中转站,流入套接字的数据首先被存放到缓冲区中,然后才能被输出数据的套接字从缓冲区中读出。描述符作为一种数据结构可将与数据流相关的套接字和缓冲区关联起来。图3为一个方向为P2U的DMA数据通道,此数据通道由8个尺寸为16×1 024的缓存及一个PIB套接字和一个UIB套接字组成。

FX3提供了多种DMA通道模式,可分为两种:一种是自动DMA通道;另一种是手动DMA通道。自动DMA通道在通道建立起来并开始运行后,固件就不再干预数据流的传输,数据将连续不断地流过自动数据通道,因不需固件干预,所以这种通道模式能提供最大的数据效率;而手动DMA通道在数据流动过程中需要CPU干预,这样就可监视或修改数据流,但有可能会降低数据的传输效率。所以设计采用自动DMA方式实现USB接口与GPIF II接口的数据传输。

3 FPGA中实现读写程序设计

本文通过FPGA采用状态机模式控制同步SLAVEFIFO接口的读写操作来实现访问FX34个线程的功能。

(1)SLAVE FIFO读操作。

IDLE:设定SLAVE FIFO的地址A0:A1;

STATE 0~3:状态自加,使FIFO地址稳定且SLCS被激活;

STATE 4:SLOE被激活,驱动数据总线;

STATE 5:SLRD和外部写信号被激活。且FIFO指针在PCLK的上升沿更新,这会启动从新寻址位置到数据总线之间的数据传输。

(2)SLAVE FIFO写操作。

IDLE—STATE 4:与读操作相同,只是在STATE 5激活sLwR信号以及外部读信号。当sLwR被激活时,数据写至FlF0和PcLK的上升沿,FIF0指针递增。

4 USB3.0采集卡实测

设计的LISB3.O样板出来后需要从多方面对其进行实际测试以验证其正确性。下面从两方面测试板卡设计的正确性。

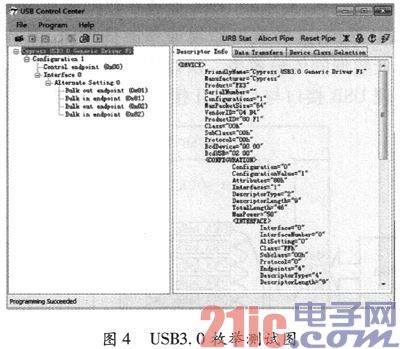

(1)USB3.0固件枚举测试。USB3.0固件能否正常工作的一个重要标志是当USB3.0控制器连接到主机上时,设备能否正常运行。设计采用Cypress主机测试软件USB Control Center对FX3固件枚举功能进行测试。经测试,测试软件成功接收了由固件发的各种描述符。图4为USB3.0的枚举成功后在测试软件上的正确显示。

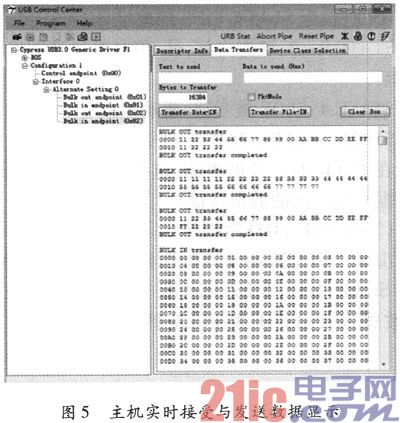

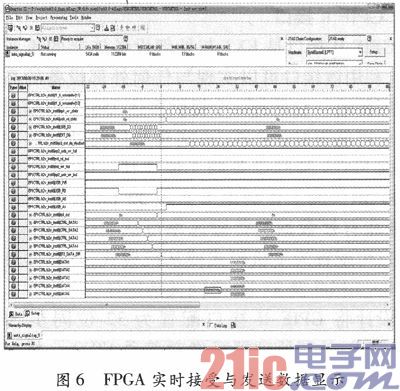

(2)USB3.0数据传输测试。设计通过EP1 OUT端点来控制EP2 IN和EP2 OUT两个端点数据的接受和发送。当通过EP1 OUT发送的最后32位数的低4位为4’h1时,FPGA接受来自EP2 OUT端点的数据;当通过EP1 OUT发送的最后32位数的低4位为4’hF时,FPGA向EP2 IN端点发送测试数据,如图5所示。图6为逻辑分析仪实时监测的PC向FPCA发送的数据显示。

5 结束语

本文介绍了USB3.0控制器的固件及FPGA读写操作的主要工作机制,并通过实验验证了所设计USB3.0板卡的稳定性及正确性。对USB3.0固件机制的深入研究是提高设计质量的前提,因而有必要对该固件作进一步研究以提高设计的效率与正确性。

关键词: FPGA USB3.0固件 SLAVE FIFO 数据通信

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码