多路SDI信号单波长无损光传输

编者按: 摘要:针对目前市场上越来越多针对SDI信号的应用需求,提出了多路SDI电信号单波长光纤传输的实现方案,就方案中出现的由于FIFO“写满”或“读空”引起的SDI信号传输误码,提出了一种基于FPGA内部PLL的可控时钟,利用该时钟作为FIFO的读时钟,实现SDI信号无损传输。 引言 串行数字接口(Serial Digital Interface,简写为SDI)是针对演播室环境提出的用单根电缆来传输数字视音频信号的方式。在SMTPE-259M标准中

接收端RFIFO的功能是从经过码速调整到30M的数据中还原出27M的数据。其主要实现流程为:采用与发端读时钟同步的时钟为RFIFO的写时钟Wrclk,读时钟采用本地分出来的符合后端SDI编码要求的27MHz的时钟Rclk_27m,由发端传输过来的DATA_valid来控制RFIFO的写使能,从而保证写入RFIFO的数据都是有效数据,RFIFO的读使能持续为“1”以保证数据的连续性。整个码速调整和恢复的信号波形如图3所示(DATA1为发端输入的原始数据,DATA2为码速调整后的同步数据,DATA3为恢复出来的数据。

采用这种方法实现起来比较简单,但是在实际测试时发现:由于SDI_27M_n这个时钟与Rdclk_30M不同步,从而造成收端进入到RFIFO的数据与RFIFO的读时钟Rclk_27M不同步,即RFIFO的读时钟与写时钟不是同步的,最后必能会造成RFIFO的“写满”或者“读空”,引起SDI信号的误码。

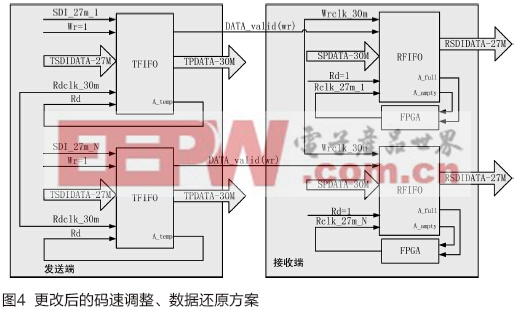

为了解决这个问题,考虑到Rclk_27M与发端的Wrck_27M_N这两个时钟虽然是异步的,但是其具体的频值偏差大约在10PPM左右,将整个系统的码速调整、数据还原修改成如图4方案。

如图4所示,发送端的码速调整、同步处理方法不变,修改接收端的数据还原部分:原方案中多个RFIFO的读时钟是由可编程分出来的同一个27MHz的时钟,更改后的方案中每个RFIFO的都由FPGA内部PLL分出,该时钟频率可以通过FPGA控制在小范围内动态地变化,具体变化形式由RFIFO的A_full、A_empty的状态来进行控制:A_full、A_empty分别为RFIFO的快满或快空标志,在系统启动时,Rclk_27M_N设置成一个初始值27MHz,随着设备工作时间的增加,由于读、写时钟的不同步,就会造成RFIFO的快满会快空,从而引起A_full(快满)、A_empty(快空)标志置位。当FPGA监测到A_full时,从而判断当前FIFO的读时钟比写时钟要慢,FIFO将空,此时通过FPGA控制内部PLL,提高其输出的Rck_27m_N时钟的频率;当FPGA监测到A_empty时,从而判断当前FIFO的读时钟比写时钟要快,FIFO将满,此时通过FPGA控制内部PLL,降低其输出的Rck_27m_N时钟的频率。通过控制RFIFO永远不会“写满”或者“读空”状态,确保SDI信号持续有效输出且不出现误码。

3 结论

通过FIFO的“快满”和“快空”标志控制来控制FPGA内部锁相环(PLL)的频率输出,从而使系统接收端RFIFO的读时钟随FIFO数据深度的变化而实时改变,确保RFIFO不会出现“写满”或“读空”的状态,解决了原来系统中由于FIFO的问题造成SDI信号误码的现象,完成了多路SDI信号的无损光纤传输。

目前通过本方案设计的多路SDI单波长光传输设备已完成研制,提供给广电系统多家单位使用,反应效果良好。

参考文献:

[1]周宇,等. 基于CPLD的异步ASI/SDI信号电复接光传输设备的设计[J]. 世界电子元器件,2009,10:58-61

[2]鲍思明.SDI串行数字分量信号格式及检测方法[J].世界广播电视,2007,9:43-49

[3]祁超,等.基于FPGA的SD-SDI视频转换接口的设计[J].仪表技术与传感器,2010,10:63-65

[4]李泉,等.用FPGA实现码速变换[J].电子产品世界,2007,4A:34-36

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码