基于FPGA的LCD大屏幕拼接系统的设计

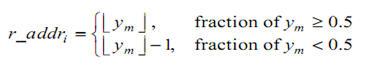

对于列或行地址计算器,输入信号决定水平与垂直方向的坐标。坐标数据包含10位的实数以及10位的小数部分。坐标数据的第9位是小数部分最重要的一位,它决定着小数部分是否大于0.5。同时由第9位控制的多路选择器控制用于输出正确的内存地址。如果输入的是列信号,那么行地址![]() ,

,![]() ,

,![]() ,

,![]() 和垂直间隔

和垂直间隔![]() 可由公式(1)到(3)得到,同理,列地址

可由公式(1)到(3)得到,同理,列地址![]() ,

,![]() ,

,![]() ,

,![]() 和水平间隔

和水平间隔![]() 能由公式(1),(2)和(4)得到。

能由公式(1),(2)和(4)得到。

3.2.2 加权系数产生单元

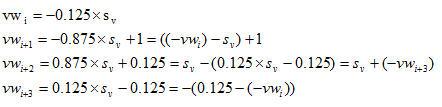

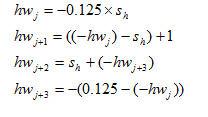

在设计的框图中,水平加权系数与垂直加权系数的计算并不是同时生产尽管它们都由公式(5)和(6)决定。因此,加权系数产生器产生水平及垂直加权系数,当控制信号为水平信号时,最终的输出为![]()

,![]() ,

,![]() ,

,![]() ,相反的,则输出

,相反的,则输出![]() ,

,![]() ,

,![]() ,

,![]() 。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。

。在延展式线性插值最大的计算量是加权系数的计算,而最复杂的运算却由最简单的两个加法器和两个减法器构成。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码