基于DaVinci™平台的网络视频解码系统分析与设计

编者按: 摘要:随着视频压缩技术的不断发展,单路1080p@60Hz分辨率的视频可以压缩到几兆进行传输,一个百兆网口可以传输多达10多路的IP视频信号。目前的服务器单纯依靠CPU进行软解码已经显得非常吃力[1];匹配高性能的服务器或者配置多台服务器却有存在高成本的压力。针对这些现状,本文设计了一个基于TI的DaVinci™平台的网络视频解码系统。验证结果显示,采样该网络视频解码系统,可以使得单台服务器增加上百路的IP视频解码,同时不影响服务器的其它性能,性能可靠且成本有很大优势。 1 TI 8

摘要:随着视频压缩技术的不断发展,单路1080p@60Hz分辨率的视频可以压缩到几兆进行传输,一个百兆网口可以传输多达10多路的IP视频信号。目前的服务器单纯依靠CPU进行软解码已经显得非常吃力[1];匹配高性能的服务器或者配置多台服务器却有存在高成本的压力。针对这些现状,本文设计了一个基于TI的DaVinci™平台的网络视频解码系统。验证结果显示,采样该网络视频解码系统,可以使得单台服务器增加上百路的IP视频解码,同时不影响服务器的其它性能,性能可靠且成本有很大优势。

1 TI 816X平台简介

DM816x DaVinci™视频处理器[2]是高度集成、可编程平台,其具有强大的视频处理能力,具备1080p@60Hz的H.264编解码能力。该平台在视频领域的应用范围非常广泛,涉及领域包含:视频编码、解码、转码和速率转换、视频安全、视频会议、视频基础设施、媒体服务器和数字标牌。

DM816xDaVinci™视频处理器包含了3个高分辨率视频和成像协处理器(HDVICP2)。每个协处理器能够执行一个1080P@60Hz的H.264编码或解码或者多个较低分辨率或帧速率的编码和解码。另外,也可完成多通道HD至HD或HD至SD代码转换以及多重编码。同时,其具备了一个数字视频输出口、一个数字视频输入口、还有一个数字视频输入输出复用口,其单个输出输入口还具备了多路视频同时分时输出、输入功能。芯片内部集成了Cortex™-A8 32位RISC处理器处理器和DSP内核,同时还集成了3D图象引擎SGX530。DM816x DaVinci™视频处理器提供了丰富的外设。视频接口有同步HD和SD模拟视频的输出和双HD视频输入;网络接口包含了2个具有GMII和MDIO接口的千兆位以太网,两路千兆网提供了多路IP视频接入的传输通道。丰富的外设集提供了控制外围设备以及与外部处理器进行通信的功能。

2 系统结构和工作原理

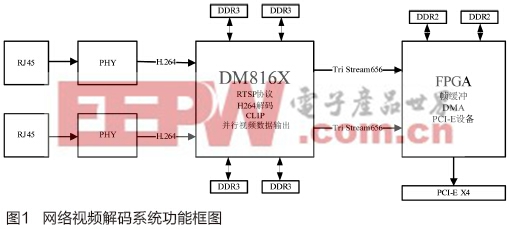

该网络视频解码系统采用DM816X和FPGA的方案,具体功能框图如图1。前端网络采用千兆网络PHY芯片,速率为10M/100M/1000M自适应。一般来说,网络IP视频从异地过来,均是通过一个路由进入到系统的前端网络采集模块;不通的路由支持支持的速率不通,同时线路的连接方式也相异,因此,我们这里采用了速率自适应和线路自适应的PHY芯片。在PHY片的另外一侧是MAC口,对应的是解码芯片的MAC口,采用的是千兆通信方式,网络时钟的速率是125MHz。从带宽上来看,前端网络可以支持高达几百路的D1视频接入,从而保证了海量视频数据接入的可能。

IP视频解码部分是采用TI的DM816X芯片为核心,外挂DDR和Flash等设备组成。在DM816x芯片上嵌入Linux操作系统,作为整个单板的主控系统,管理各种外设,包括网口、DDR、可调电源模块和Flash等,还可通过对FPGA模块进行寄存器读写来管控后端的视频处理环节。目前网络视频大部分带有数据打包协议,我们这个系统可以支持标准的RTSP协议,同时也支持非标准的数据包,只有给出前端打包协议,就可以自定义解网络数据包。网络解包后,得到H.264码流后,便送入到816x内置的解码器(HDVICP2)进行解码;解码后的数据可以利用816x的视频处理系统进行裁剪、缩放和叠加。经过一系列处理后,将图像通过816x的2路视频数据输出通道进行输出。虽然在物理通道上只有2路视频输出口,但是,通过软件编程,可以采用Tri Stream 656的方式,分时输出6路1080p@30Hz的视频信号到视频缓冲和显示处理模块。

视频缓冲和显示处理模块主要由FPGA芯片和位于服务器上的显卡组成。经过解码芯片处理后的视频数据进入到FPGA后,还不能直接进入到显卡。首先,逻辑芯片需要对视频数据进行帧缓存,把数据先放进DDR2中,在DDR2中建立3帧图像存放空间,通过控制读取视频帧的速度达到帧率调整的目的。逻辑内部的PCI-E设备传输数据是采用串行传输,而从缓冲区出来的是并行视频数据,这个时候需要对视频数据进行并串转换。在服务器端的显卡,通过驱动软件可以开辟出一块显存区域用于存放并显示视频数据。一般和PC系统进行数据交互采用DMA方式是最为高效直接的,因此,我们将开辟处理的显存区域映射到PCI-E设备中,通过逻辑程序把视频数据通过DMA方式放入到映射区域。这样,就相当于直接把视频数据放入到显卡中进行显示。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码