使用MATLAB和Simulink算法创建FPGA原型(一)

ebkit-text-size-adjust: auto; orphans: 2; widows: 2; webkit-text-stroke-width: 0px"> 为了明智确定所需的小数位数,在开始HDL编码过程之前,工程师需要某种方法来比较浮点仿真结果与定点仿真结果。增加小数位数可以减小量化误差;不过,这种方法需要增加字长(区域增多、功耗升高)。

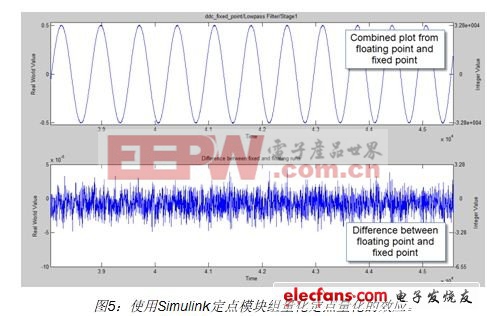

例如,图5展示了DDC滤波器链路中低通滤波器第一阶段浮点与定点仿真结果的差异。这些差异是因定点量化所致。上方图形显示了浮点与定点仿真结果的重叠效果。下方图形显示了图中每一点的量化误差。工程师可能需要根据设计规范来增加小数位数以减小由此引出的量化误差。

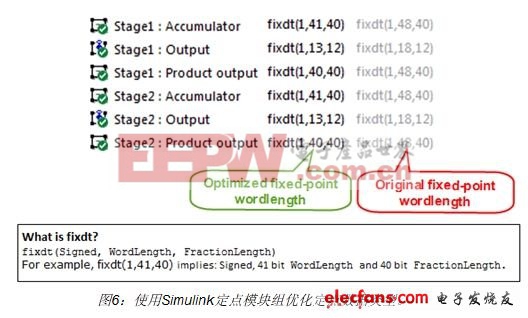

除了选择小数位数之外,工程师还需要优化字长,实现低功耗和区域优化的设计。

在DDC案例研究中,工程师使用Simulink定点模块组将部分数字滤波器链路的字长减少了8位之多(图6)。

1

2

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码