基于32位微处理器AEMB的SoC系统验证平台设计

3.4 中断控制器与时钟定时器的配置

中断控制器主要用于接收外部中断源的中断请求,并对中断请求进行处理后再向CPU发出中断请求,等待CPU响应中断并进行处理。在CPU响应中断的过程中,中断控制器仍然负责管理外部中断源的中断请求,从而实现中断的嵌套与禁止。在本设计中,中断控制器的逻辑结构如图2所示。所采用的中断控制器主要负责接收片内IP核及片外器件所发出的中断请求,然后根据一定的优先级与规则将中断发送给微处理器。微处理器可以通过设置与读取相应的中断寄存器来管理查看中断优先级与中断状态。

图2 终端控制器逻辑结构

时钟定时器主要是作为操作系统的时钟滴答定时器,本质上就是一个简单的计数器。在每个系统时钟来到时计数器会自动加1,当计数器的值达到设定数值时便产生1次时钟中断。PTC是OpenCores组织发布的一个支持Wishbone总线接口的脉冲定时计数器。其不仅可以作为时钟定时器,还可以通过配置寄存器的设置产生PWM脉冲输出。本SoC系统中主要是使用PTC的定时器功能。

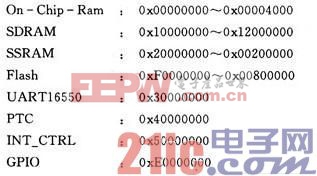

3.5 地址空间的分配

根据DE2-70开发板上各器件的特点与AEMB微处理器的中断例外向量表及wb_conmax的逻辑实现,系统地址空间分配结果为:

4 SoC系统的FPGA综合实现

针对DE2-70开发板在进行SoC系统的FPGA综合时选用CycloneII系列器件EP2C70F896C6。系统时钟频率预设为50 MHz,不加额外约束条件下进行综合,综合后的逻辑资源占用报告如图3所示。

图3 SOC系统FPGA综合后逻辑资源使用情况

通过时序分析报告可知,该SoC系统在满足时序的前提下,系统实际运行频率可达到65.31 MHz。

5 SoC系统验证平台软件支持

考虑到SoC验证平台所包含的硬件部件与该平台的具体应用,系统软件主要构成如图4所示。Mini Bootloader负责应用程序从Flash器件向程序运行空间的加载。在DE2-70开发板上,借助于NiosII开发工具与开发板自带的基于NiosII的SOPC硬件系统,烧写Flash很方便。系统启动时可以从Flash开始启动,完成应用程序的拷贝后再跳转到主程序运行的存储器空间。在本系统中,为了使编程更加方便,将拷贝程序放在片上RAM中存储。系统从片上RAM开始启动,完成应用程从Flash到SDRAM的拷贝之后,跳转到SDRAM开始执行应用程序。

图4 SoC系统软件支持

AEMB微处理器在指令上与MicroBlaze达到99%的兼容,而后者的应用程序及操作系统的开发已经有非常成熟的范例。操作系统的移植主要是完成对硬件地址空间的修改与操作系统一些底层初始化代码的编写。最终在该SoC系统验证平台上完成了μC/OS-II的移植工作。

结 语

本文基于32位微处理器AEMB设计了一款SoC系统验证平台,给出了SoC系统经过FPGA综合后的逻辑资源占用情况,以及系统能够运行的最高时钟频率。该平台已在台湾友晶公司的DE2-70开发板上完成了FPGA验证。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码