基于FPGA的室内智能吸尘平台设计

3 程序设计要点

将程序分为硬件程序设计和软件程序设计两部分,硬件程序设计要对硬件电路进行时序仿真以确定达到调试的效果。

3.1 硬件程序设计与仿真

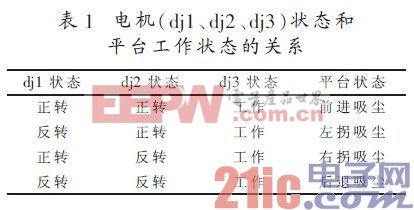

平台主要通过传感器和碰撞开关产生输入信号,通过FPGA处理信号,最后FPGA把处理后的信号传到电机,由电机来完成一系列的动作,如表1所示。所以其逻辑设计是实现智能的关键。

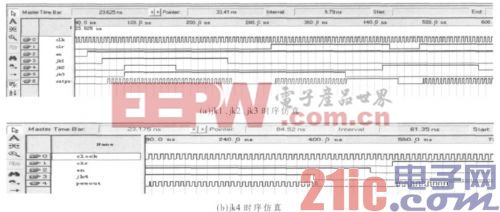

结束硬件选型后,利用Quartus II搭建硬件原理图,编译后对jk1、jk2、jk3、 jk4进行时序仿真,分析时序关系,估计设计的性能并检查和消除竞争冒险[7-9]。仿真结果如图3所示。

时序仿真图中,clk为输入PWM信号,clr和en两个模块的片选信号是由FPGA的SoPC通过软件C语言控制。当jk1=0、jk2jk3=1时,output(PWM控制信号)会出现一段等于0之后产生20个波形。需要说明的是:图3(a)时序仿真图中,output出现一段PWM后出现低电平后接着出现了20个PWM,说明平台在正常前进遇到jk1=0、jk2jk3=1时,会停车一段时间接着左拐或者右拐20个PWM角度。驱动器用的是4细分,输出1个PWM波形步进电机会转动0.45°,应该旋转90°但是波形个数为:n=(90/0.45)=200个,在此用20个代替200个说明问题(图3(b)的波形个数都会以此情况说明)。

由图3(b)可以看到前段时间jk4为高电平,pwmout输出正常脉冲,说明此时平台处于正常吸尘状态。后段时间jk4变为低电平,pwmout时延后输出一小段脉冲,说明此时平台检测到楼梯,停车一段时间后调整方向。

3.2 软件程序设计

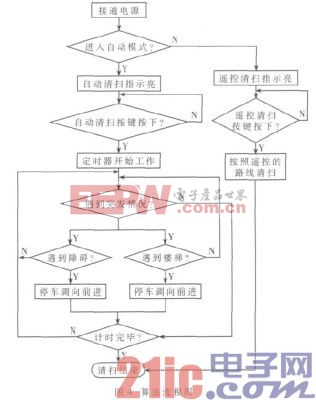

硬件设计调试完成后,还要进行软件系统设计。在C语言文件中编写C程序进行SoPC的编程[10]。平台工作总体算法流程如图4所示。平台接通电源,首先初始化进入自动清扫和手动遥控清扫二选一模式;当选择自动清扫模式时,通过键盘输入平台自动清扫工作时间,在清扫过程中通过传感器判断是否遇到障碍物或楼梯并进行处理。通过中断,时刻查询是否到达设置时间,如果没到,则程序返回运行;如果设置时间到,则程序结束,平台停止工作。当选择遥控清扫时,平台运动受操作者的控制。

通过硬件选型、搭建调试和软件语言的编写调试,成功地制作出了简易平台,实现了既定的各种功能。相比市场上的同类产品,其结构更简单、成本更低、灵活性和扩展性更强,为研究者开发更多功能提供了一个硬件支持的平台,具有实用价值。随着微处理器的不断进步和传感技术的发展,其性能可不断改进,成本也可不断下降。但在仿真和实现过程中发现其具体的流程算法不够严谨,日后有必要继续对其进行改进。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码