使用 PlanAhead Design 工具提高设计性能

PlanAhead 软件提供了一种解决方案

越来越多的客户在赛灵思® PlanAhead™ 设计分析工具提供的层次化设计方法学中找到解决方案。PlanAhead 软件为 FPGA 设计流程增加了可视性和控制。通过解决物理方面(介于逻辑综合和实现工艺之间)的问题,您可在您的设计结果中实现性能的提高。

虽然先进的 FPGA 综合产品为几百万门设计提供极高的自动优化水平,许多设计者仍需要具有更多启发性的技术,以达到最佳性能目标。通过提供早期分析和布局规划 (floorplanning)功能,PlanAhead 设计工具可以施加物理约束,以帮助控制设计的初始实现。实现后,PlanAhead 软件可以分析布局和时序结果,以改进用于完成设计的布局规划。您可以使用来自导入结果的物理约束,在后续实现尝试期间锁定布局。这些约束可用于创建可重用 IP,连同锁定布局,一同用于其它设计。

PlanAhead 设计方法提供了性能、生产力以及结果的可重复性。凭借其层次化设计流程,PlanAhead 软件可让您减少运行 PAR 然后返回 RTL 与综合的反复次数。相反

,您可以分析设计并在实现之前解决物理方面的问题。

更少的时间,更快的结果

PlanAhead 用户通常可以实现 10-15% 的性能提升,有些用户甚至可以实现更高。此外,设计者还发现他们可以在一个紧凑的器件中额外加入 10% 的逻辑。更快的性能与更高的利用率的结合意味着可以使用更小更便宜的器件,或者以更低的速度等级实现设计目标。

PlanAhead 设计工具可在缩短总设计时间的同时,还在结果中增加一定的一致性水平。通过利用以前的布局规划或增量设计技术,您可以以更少的时间执行设计反复,实现可重复的结果。您还可以利用成功结果,将它们锁定下来或在其它设计中重用。

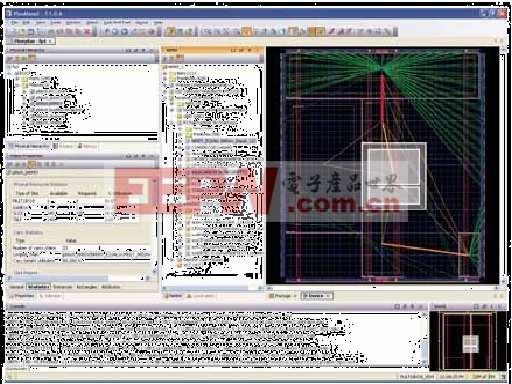

解决真正棘手的性能问题所需要的绝不仅仅是增加新的菜单项或脚本能力。PlanAhead 软件通过使用各种视图(见图 1)展示设计数据,提供了一个完整的环境,使该层次化方法实现交互并易于使用。这些独立的视图可以相互结合使用,从而允许您快速识别和浏览关键设计对象和信息。

图 1:PlanAhead 软件提供了设计的不同视图,以显示物理层次、属性、网表与约束、器件封闭引脚、原理图及更多。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码