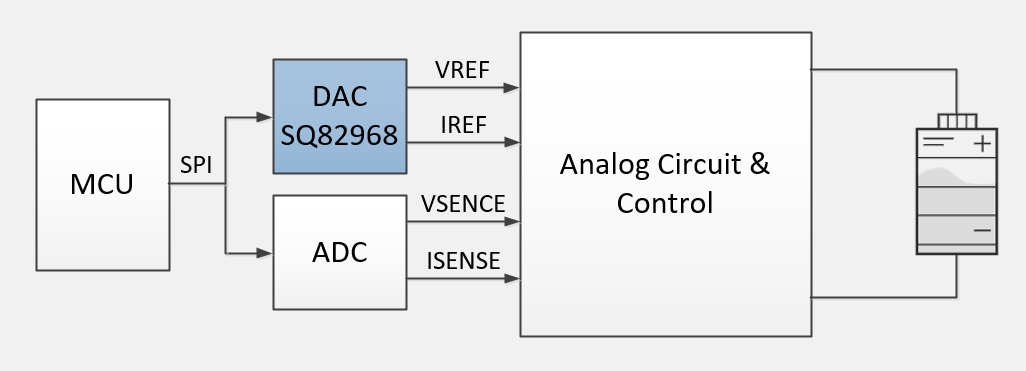

DAC及其缓冲器有助于提升系统性能与简化设计一

构

积分非线性: 积分非线性(INL)衡量DAC的理想输出与排除增益和失调误差之后的实际输出之间的最大偏差。与R-2R网络串联的开关可能会影响INL.乘法DAC一般采用NMOS开关。当用于电压开关模式时,NMOS开关的源极连接至基准电压,漏极连接至梯形电阻,栅极由内部逻辑驱动(图6)。

性能特点

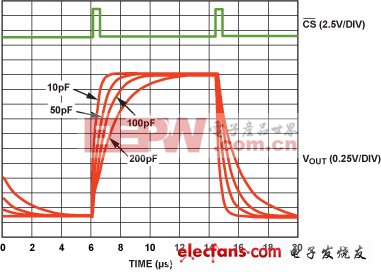

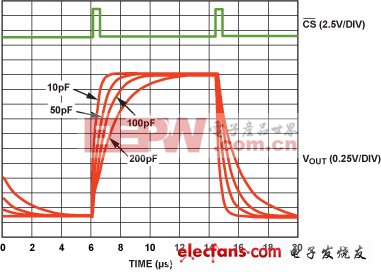

建立时间: 图4和图5比较了乘法DAC在电压模式下的建立时间以及AD5541A的建立时间。当输出上的容性负载最小时,AD5541A的建立时间约为1?s.

图4. 乘法DAC的建立时间

图5. AD5541A的建立时间

噪声频谱密度: 表1比较了AD5541A和乘法DAC的噪声频谱密度。AD5541A在10kHz下的性能略占优势,在1 kHz下优势非常明显。

表1. AD5541A与乘法DAC的噪声频谱密度

图6. 乘法DAC开关

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码