适用于HDTV应用的8位DAC

NSFORM: none; COLOR: rgb(0,0,0); TEXT-INDENT: 0px; WHITE-SPACE: normal; LETTER-SPACING: normal; BACKGROUND-COLOR: rgb(255,255,255); orphans: 2; widows: 2; -webkit-text-size-adjust: auto; -webkit-text-stroke-width: 0px">

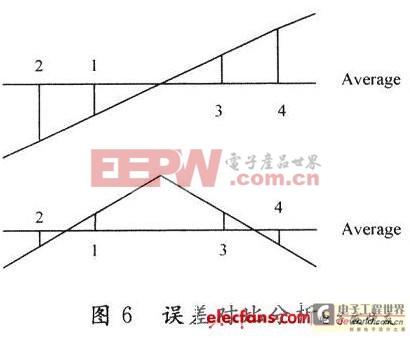

根据图6所示梯度误差与对称误差的对比,在单位电流源矩阵中采用层次式对称开关序列的布局,很好地减少了误差。

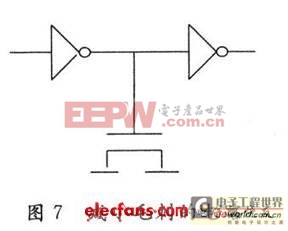

3.2 减少毛刺的电路

在基本的电流源单元,输出信号将是比较稳定的。在这个设计中电流源由开关电路输出信号控制,但输出信号不是足够的准确。因此,为了补偿这个缺点,同时改进电路的SNR,需要使用减少毛刺电路,如图7所示。

4 实验结果

该文设计的DAC基于O.25 μm CMOS技术,8位高速DAC适用于高清晰视频使用,并且使用TG晶体管和电路级数的数量可以明显减少,同时使用TG结构也可使电路延迟时间有效地减少,且毛刺也被大大减少。结果显示:这个设计可以达到1.5 GHz采样率和21 mW低功耗。

具体参数指标如表2所示。

5 结 语

本文提出基于新型传输门(TG)结构组成的电流源单元矩阵、译码逻辑电路和一种适用于高清晰视频使用的高速8位CMOS电流舵数/模转换器(CS- DAC)。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码