基于FPGA的大屏幕LED点阵显示系统设计

二、接收卡控制系统单元模块设计

(一)时钟控制模块

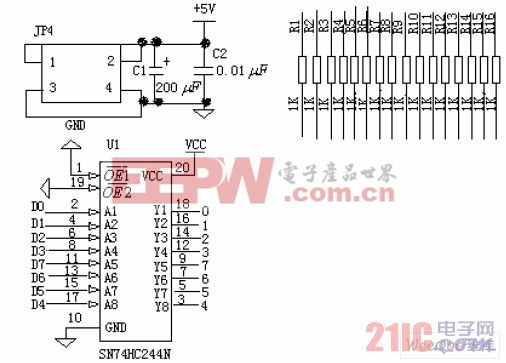

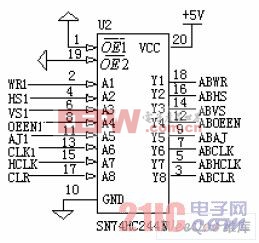

1. 行计数时钟和扫描控制信号

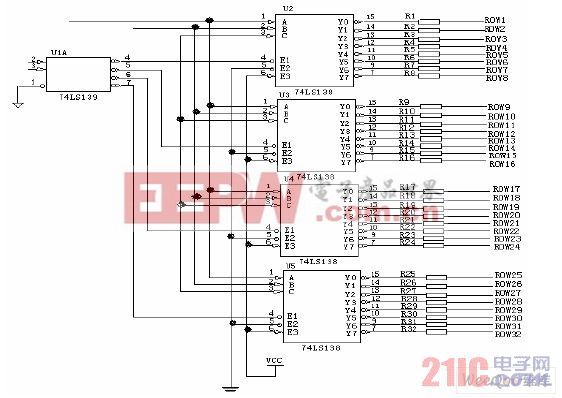

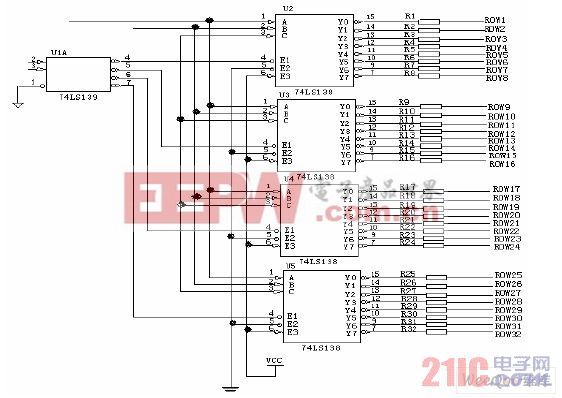

采用行扫描的,必须产生行扫描控制信号。如图 2所示的row[4..0]是行扫描控制信号,用它接一个 2-4 译码器和四个 3-8 译码器来产生 32个行选信号,构成 1/32 扫描方式的显示屏。Hclk为行计数时钟,也可以称为行锁存时钟。

图2 行驱动模块原理图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码

二、接收卡控制系统单元模块设计

(一)时钟控制模块

1. 行计数时钟和扫描控制信号

采用行扫描的,必须产生行扫描控制信号。如图 2所示的row[4..0]是行扫描控制信号,用它接一个 2-4 译码器和四个 3-8 译码器来产生 32个行选信号,构成 1/32 扫描方式的显示屏。Hclk为行计数时钟,也可以称为行锁存时钟。

图2 行驱动模块原理图

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码