基于MCU/FPGA的多功能正弦信号发生器的设计

3 电路调试及仿真

电路调试采用计算机仿真和硬件调试相结合的方式,以QuartusII 5.0为设计环境,用Verilog HDL硬件描述语言编程,完成各个功能模块的设计,并对设计好的各个模块进行仿真测试,再将各个模块相互连接。分配好FPGA的各个引脚后,对文件编译并将生成文件下载到FPGA中,完成设计。

3.1 软件仿真

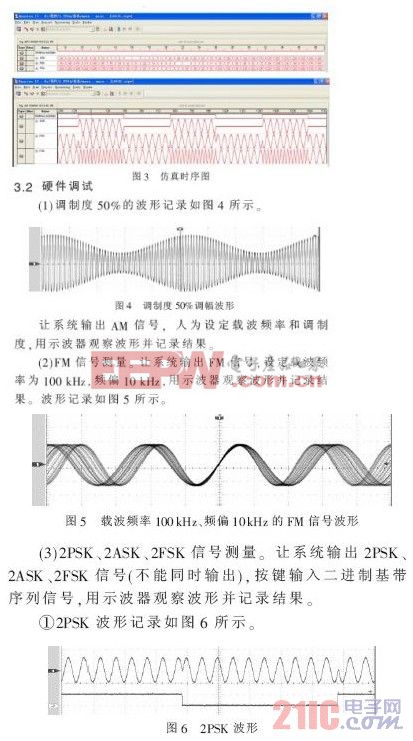

在FPGA内编译后,仿真时序如图3所示。

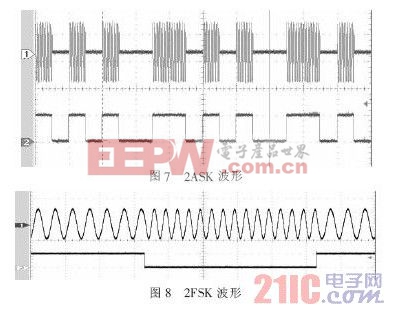

②2ASK波形记录如图7所示。

③2FSK波形记录如图8所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码