如何在后版图网表上优化泄漏功率

此外,假设在下列单元上换回原始形式会导致:

● 单元D和B的单元延时将减少30 ps

● 单元C的单元延时将减少35 ps

● 单元A的单元延时将减少45 ps

很明显,换回单元A就可以解决3个端点 (见图2) 的违反问题,不必分别交换每个端点的单元 (D 和 B或C)。

结果

这种方法最初是在CEVA内部开发的一款DSP产品CEVA-X1622 DSP内核上执行。

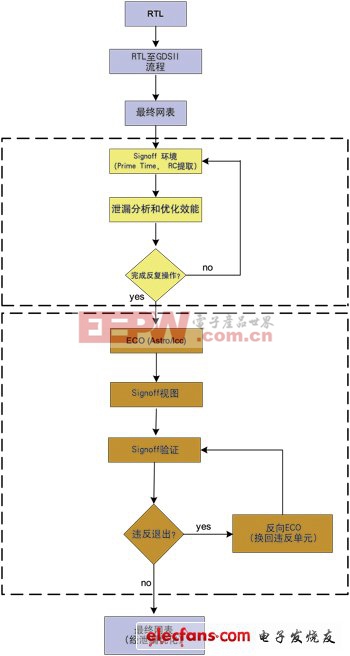

其设计规模在450,000门左右。流程主要部分的总体运行时间大约为12个小时 (即运行一个晚上) (见全流程概述图2的黄色部分),而使ECO结果与Signoff相符合的Signoff运行时间很少 (见全流程概述图2的褐色部分)。

附录

多模工作

当工作在一个以上的模式中时,必需针对每一个模式分别执行优化,且交换清单中不能包括其它模式的单元。

对于每一个模式,这种方法都生成ECO档,并将之附加到包含了所有模式交换的全局文件中。然后,在后版图设计中执行单个ECO,并对每一个模式执行一次完整的RC提取 + STA运行。

由于在某个模式中某些路径可被视为“无约束路径”(unconstrained paths),故必需予以分离,但在其它模式中它们可能是时序约束的。这种情形可能导致虚假交换,增加修正这些违反所需的总体运行时间。

以左图为例 (图5);这是控制受约束路径的Scan_enable信号。在功能性模式中,该信号具有恒定值,因此PrimeTime看不到扫描模式路径 (红色)。这时,PrimeTime会把红色路径上的所有单元交换到高Vth,从而可能造成max_transition违反,甚至建立违反。

把这些模式分离开来可以防止这种情况发生,并改善总体运行时间和真实交换数目。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码