基于PSoC5 UDB的DMA传输

2), DMA配置

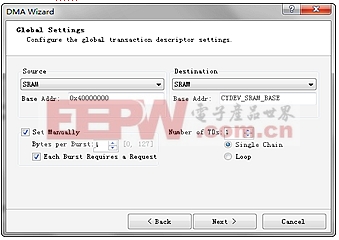

DMA配置成从datapath的FIFO处搬运数据到SRAM中,FIFO满标志边沿触发。采用burst模式,每次burst 4个字节数据,4个DMA的配置相同。唯一要注意的是DMA的源地址和目的地址采用32位模式,并且分高16位和低16位,在PSoC5中datapath FIFO和SRAM不在同一个地址区,所以其高16位地址(图9的Base Addr)也不相同,要分别配置,如下图9所示:

图9, DMA地址和burst配置

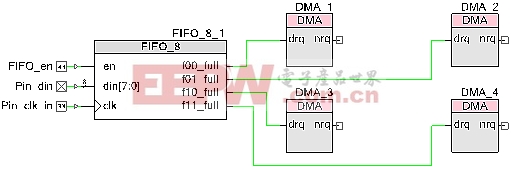

3), 在Creator中的原理图

将FIFO_8模块和DMA模块结合起来,用datapath FIFO的满标志连接DMA的drq引脚,其原理图如图10所示:

图10, DMA传输原理图

经测试,该方案能稳定的从外部采集数据并保存在SRAM中,当PSoC5的BUS_CLK为63MHz时其数据传输速度可达15MHz。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码