基于FPGA的VGA可移植模块终极设计

一、VGA的诱惑

首先,VGA的驱动,这事,一般的单片机是办不到的;由于FPGA的速度,以及并行的优势,加上可现场配置的优势,VGA的配置,只有俺们FPGA可以胜任,也只有FPGA可以随心所欲地配置(当然ARM也可以,应用比较高吧)。

初学者就是喜欢看炫的效果,往往会忍不住想玩。尤其玩FPGA的,没玩VGA就感到跟单片机没啥提升,因此VGA的驱动也不得不讲。Bingo当年也是如此。挡不住VGA的诱惑,初学者问Bingo VGA问题的人也是灰常的多,也许一般教科书理论太强,实际应用不是很身后,在此Bingo用浅显易懂的语言来讲述VGA的驱动原理,以及通过设计一个可移植模块的应用来讲述。

二、VGA驱动原理

此处Bingo不参考任何资料,用当年已学的知识,用浅显易懂的语言讲述。

2、VGA时序

VGA其实就是相当于一块芯片,跟单片机驱动IC一样,满足一定的时序,便能驱动起来。

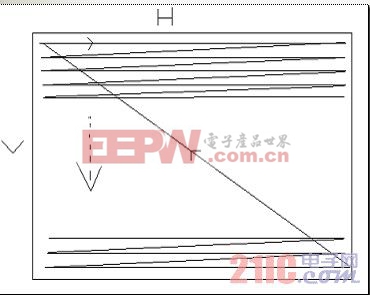

(1)扫描轨迹

VGA的扫描其实很简单,大致轨迹如下所示:

没扫描完一行,从新开始下一行;每扫完一场,重新开始下一场。相信你应该看的懂。

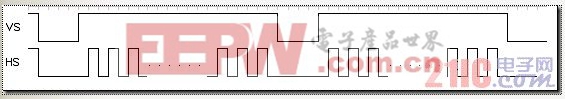

(2)行场扫描

以下是行扫描,场扫描HS,VS时序图

如上如所示:VGA一直在扫描,没一场的扫描包括了若干行扫描,如此循环。

(3)VS时序深入分析

VS时序如下所示:

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:场消隐期 即同步,相当于还原扫描坐标吧

B~C:场消隐后肩 相当于准备开始扫描吧

C~D:场显示期 扫描中,数据有效区域

D~E:场消隐前肩 完成扫描,相当于准备同步

(4)HS时序深入分析

可见时序的循环,可被划分为a,b,c,d4个时期。这四个时期定义如下:

A~B:行消隐期 即同步,相当于还原扫描坐标吧

B~C:行消隐后肩 相当于准备开始扫描吧

C~D:行显示期 扫描中,数据有效区域

D~E:行消隐前肩 完成扫描,相当于准备同步

综上描述,我们只要知道每个时期的时间,便可以表示出VGA的时序。而FPGA的工作是由固定频率的时钟触发的,因此某固定时间可以用n次触发来表示。因此我们很容易就想到了FPGA常用的计数方法:比如说行扫描,我们计数0~H_total-1。用另一个进程将其划分为4个时期,安标注分配。其实这相当于状态机。

以下是固定分辨率1024*768 60fps下HS,VS的标准:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码