基于PCIe总线的航空视频采集记录系统的设计

摘要:PCIe总线不仅硬件接口简单,软件和PCI总线完全兼容,而且传输速度数十倍于PCI总线。针对载机任务系统实时视频采集记录的需求,设计了一种基于PCIe总线的航空视频采集记录系统,利用现场可编程逻辑器件(FPGA)实现了视频数据流的编解码和PCIe桥接口的设计,简化了硬件接口设计,提高了系统的工作效率。系统在某型数字化对抗训练系统中的实际应用表明该设计实用可行。

关键词:PCIe总线;视频采集;硬件设计语言;INDS

0 引言

航空电子系统之间以传递状态数据和控制数据为主,因为数据量不十分巨大,对传输速率要求并不高。例如,最流行的航空总线ARINC 429和1553B总线,速率分别是100kbps和1Mbps。而随着飞行训练强度和精度的提高,飞行试验和训练过程的多通道视频画面需要实时记录下来以便进行事后分析评估和系统设计改进。与传输状态控制信息相比,这些视频数据是巨量的,对航电系统的海量存储和数据高速传输都提出了更高的要求。本文提出一种航空视频采集记录系统的设计方案,采用速率高达2.5Gbps的PCIe总线构建系统,PCIe总线既有高速的数据传输能力,又有良好的外设接口,有利于大容量信号的实时传输。有效解决了机载多通道视频数据的实时采集与记录,为航空训练任务系统的事后评估和性能分析改进提供了便捷的手段。

1 系统的方案设计

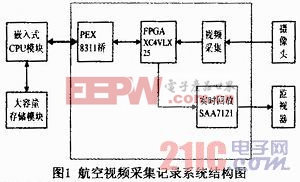

在航空视频采集记录系统中,摄像头把载机任务系统的实时画面视频数据按预定格式组帧,通过LVDS信号总线传输给视频采集模块;经过视频采集模块对LVDS信号电平进行变换处理后,将单端视频数字信号送给可编程逻辑器件(FPGA)进行视频解码处理。解码后的数字视频,一方面通过SAA7121视频编码器直接送给监视器,让飞行员实时掌握训练情况与效果:另一方面通过高速PCIe总线传送给嵌入式CPU模块进行视频数据压缩存储,供事后分析。航空视频采集记录系统总体结构如图1所示。

2 系统的硬件设计

系统的硬件设计主要集中在各个功能模块的电路设计上,是软件设计和系统调试的平台基础。硬件设计应该保证系统运行的高可靠性,在满足要求的前提下,尽量减少可编程逻辑、系统软件的设计与调试的难度。

2.1 视频数据采集

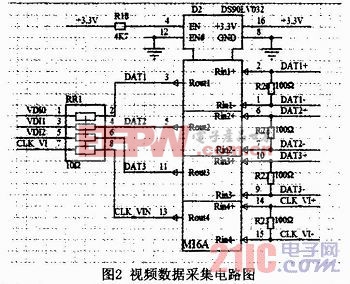

摄像头摄录的视频数据以LVDS差分电平信号进行传输,需要进行电平信号转换才能进行后续视频信号的记录处理。摄像头传输的视频数据包括4对LVDS差分信号,CLK+/CLK-是采集数据的时钟,其余3对差分信号包含着像素灰度。差分信号经过DS90LV032转换,变成4个单端的数字信号,供后面的电路处理。视频采集电路如图2所示。

因为视频数据频率较高,经过转换后的单端信号应该端接10 Ω的电阻以抑制反射,提高信号稳定性。

2.2 视频解码和处理

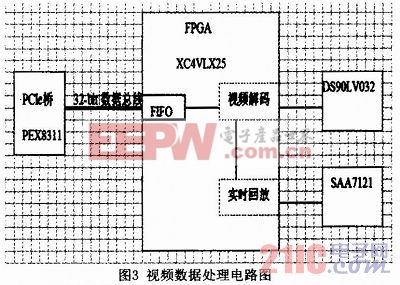

对前端采集的视频数据,必须进行处理才能实时显示和压缩存储。由于视频数据量大,为达到最流畅的快速处理,应该由硬件逻辑直接进行数据处理。视频数据的解码和处理主要由FPGA完成,也是可编程逻辑设计的主要任务。

当前端DS90LV032将经过信号转换以后的视频数据传输给FPGA,由FPGA完成视频信号的解码还原、格式转换后同步传输给CPU模块进行实时记录和实时回放视频模块。FPGA视频数据处理的硬件接口设计如图3所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码