如何实现微控制器与FPGA的接口设计

因为处理器专门负责维持PIO工作,所以处理时间消耗很大。虽然CPU是从事数据传输,它还是不能做别的事了。因此,这一解决方案有可能使系统处理陷入瘫痪。DMA不可能使用的PIO接口,所以程序员必须限制的数据带宽,以便其他任务能够与MCU进行通讯。例如,如果有一个常规的进程要求100 %的处理器运行周期,同时又要与FPGA进行串行(SPI,USART或TWI)通信(读或写),那么这两个进程必须有一个要等待。如果发送到或接受来自FPGA的数据没有及时的存进缓冲区,那么到下一个字节/字数据时可能会溢出。从本质上讲,嵌入式处理器成为受??赖的数据移动硬盘。

通过外部总线接口连接(EIB)

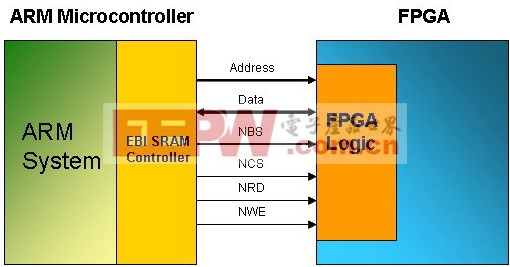

许多32位微控制器有一个外部总线接口(EBI)模块,它是为外部设备和基于ARM设备的存储控制器之间传输数据而设计的。这些外部存储控制器能够处理几种类型的外部存储器和外围设备,如SRAM,PROM,EPROM,EEPROM,flash和SDRAM。只要FPGA可以处理预定义存储器接口,EBI也可用于FPGA的接口。在EBI中使用静态存储器接口(SRAM)对于FPGA通信来说是最好的,因为它设计简单,且大多数设计者都熟悉它。至于PIO接口, FPGA不得不包含一个模块,用来理解SRAM时间,并能产生一个响应返回微控制器(图4)。

图4 EBI-SMC接口

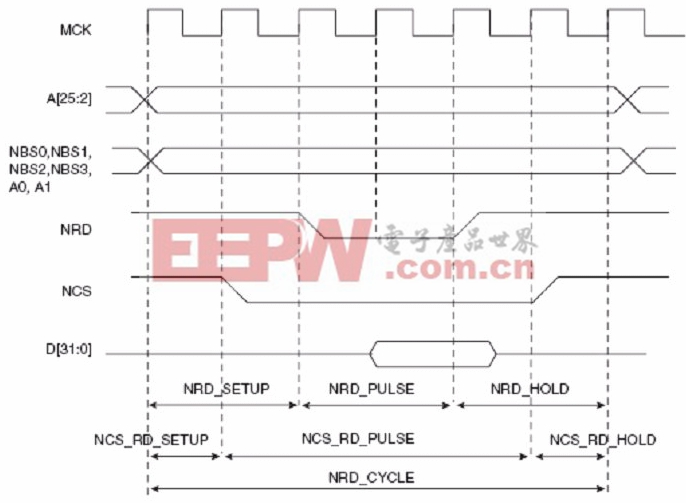

图5显示了EBI读SMC存储器接口的标准时间,而图6显示了其标准写周期。

图5 EBI-SMC读周期

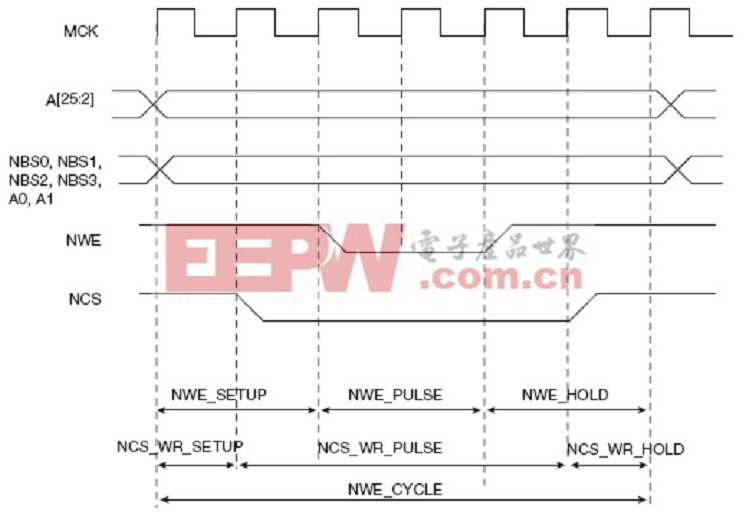

图6 EBI-SMC写周期

注意:这些时间波形是默认的SMC规格。所有可编程参数显示都基于外部设备的速度。

EBI的接口速度比PIO块,是因为EBI有其自己的I / O,且大部分的信号是并行的。但是,如果外部设备很慢或引入等待状态, EBI的速度优势可能会受到损害。

跟PIO接口一样, EBI接口必须由处理器或其他的主AHB来驱动。因此,实现带宽的EBI的还依赖于软件,并取决于它可以利用多少处理器时间。当然,可能受到带宽的限制。这又可能限制了嵌入式处理器旨在实现的其他系统功能。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码