基于ARM和CPLD的嵌入式视觉系统设计

由图1可见,微处理器的总线接在CPLD上,在对功耗有严格要求的场合中,只需要在CPLD中,将OV6620的同步时序信号所对应的引脚与LPC2214连接在CPLD上的中断引脚相连,系统就可以转换成方案1的形式。对CPLD而言,引脚相连的仅仅是组合逻辑,降低了功耗。方案1的具体工作过程可见参考文献[1]。

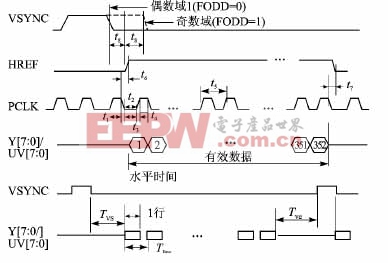

图2 OV6620输出时序图

在Verilog语言中,对上升沿的检测是通过always语句来实现的。例如检测时钟信号cam_pclk的上升沿:

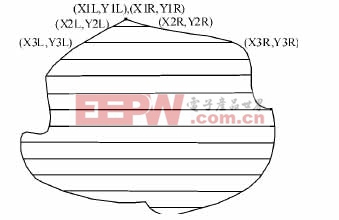

图3 行处理得到的线形图

根据得到的结果,可以计算出更多关于跟踪物体的信息:

① 计算区域面积。计算每条线段的长度l(n),然后将l(n)进行累积叠加,即可获得跟踪区域面积值S。![]()

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码