基于FPGA的SPI总线在软件接收机上的应用

3.2 模块设计

3.2.1 分频模块

由于SPI总线协议要求的SCK时钟频率与FPGA时钟频率不一致,所以对基带时钟进行分频。本文中,基带时钟频率为40 MHz,SPI总线时钟频率为1 MHz,故需要进行40倍分频。

3.2.2 发送数据模块

在片选信号拉低之前,时钟信必须为低电平。当片选信号拉低后,SCK开始工作,然后写八位地址,接着写32位数据;发送操作结束后,片选信号拉高,SCK=0。代码如下:

3.2.3 接收数据模块

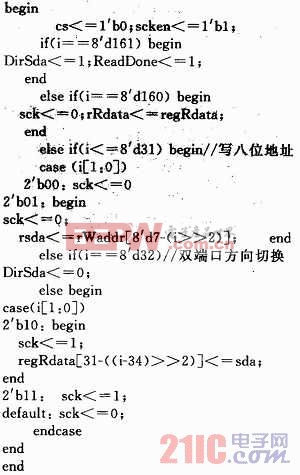

当片选拉低后,SCK=0,同时写八位地址并且使SDA为高阻,再读32位数据;当片选拉高时,CS=1,SCK=0,此外,在片选信号拉低之前,SCK必须为低电平。代码如下:

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码