基于FPGA的IEEE 1394b高速数据传输系统

当FPGA为PCI主设备时,它通过PCI-Avalon桥发起PCI主传输,如图3所示是PCI主模式写交易的仿真时序。当FPGA为PCI从设备时,链路层控制器是PCI命令的发起者,并由PCI-Avalon桥自动进行分析,将PCI总线上的命令转化为相应的Avalon总线信息,图4所示是PCI从模式配置读写仿真图。

2 嵌入式软核Nios ll的设计

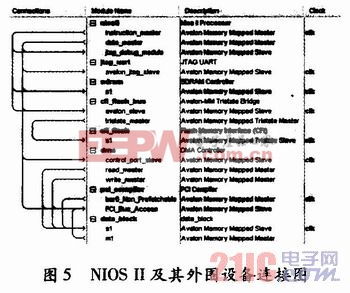

Nios II是Ahera推出的32位RSIC嵌入式处理器,根据用户的需求有Nios II/f(快速)、Nios II/s(标准)以及Nios II/e(经济)3种可配置的方案。Nios II还支持片内调试和指令定制,具有较大的灵活性和可扩展性,而且许多常用的标准外设接口已经以IP核的形式集成在了SOPC Builder开发环境中,用户如需要则可直接调用,缩短了开发周期和成本。根据应用需要,本系统将Nios II配置成快速型,时钟频率为100 MHz。Nios II与各种外设通过Avalon总线连接,具体的连接关系如图5所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码