基于FPGA的CAN总线控制器SJA1000软核的设计

1 读写模块

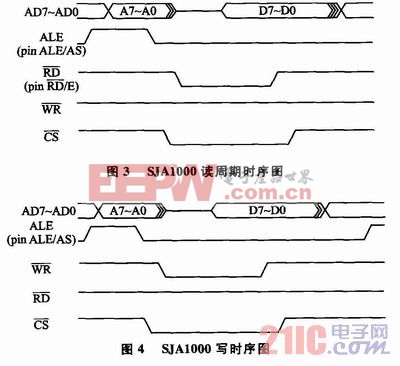

由SJA1000的数据手册可知,SJA1000提供的微处理器接口信号有地址数据复用总线AD0~AD7、地址锁存信号ALE、片选信号完成对SJA1000特定寄存器的命令字写入。与写操作相似,只需严格按照时序,将ALE、

设计时采用状态机的形式,由读写时序图可以看到,与SJA1000读写相关的控制信号有ALE、![]() 、

、![]() 、

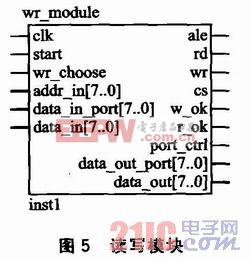

、![]() 。无论读写,都必须先输出地址,由接口控制逻辑模块输入地址。AD[7..0]是数据双向流通的,由双端口模块组成,读写模块与之相接口,输入、输出设计分开。读写模块在与接口控制逻辑接口模块相连接时,输出的数据与输入的数据也设计分开。同样读写模块的开启信号与读/写选择信号也由接口控制逻辑给出。由QuartuslI生成的读写模块如图5所示。

。无论读写,都必须先输出地址,由接口控制逻辑模块输入地址。AD[7..0]是数据双向流通的,由双端口模块组成,读写模块与之相接口,输入、输出设计分开。读写模块在与接口控制逻辑接口模块相连接时,输出的数据与输入的数据也设计分开。同样读写模块的开启信号与读/写选择信号也由接口控制逻辑给出。由QuartuslI生成的读写模块如图5所示。

在IDLE状态等待,当4个功能模块中需要使用读写功能时,由接口控制模块控制使该功能模块与读写模块连接,相应的功能模块输出地址到读写模块,接口控制模块配合给出读写选择信号,然后进入address状态,输出地址到SJA1000,判断读写选择信号后,进入读状态或者写状态。在读写子状态只需按照时序图输出ale、cs、wr、rd的值即可,标志信号w_ok表示一次读/写完成。

在SJA1000的读写过程中,对各个信号的持续时间有着严格的要求。以读操作为例,![]() 信号的有效持续时间必须最大为50 ns,因此在设计中,

信号的有效持续时间必须最大为50 ns,因此在设计中,![]() 信号保持低电平的时间可以比这个时间长。

信号保持低电平的时间可以比这个时间长。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码