基于FPGA的扩频测距快速捕获仿真研究

2 主要模块仿真结果

2.1 PH码产生模块

本设计选取的PN码为63位,本征多项式为x6+x+1。该PN码产生器由VHDL语言编写,其仿真结果如图2所示。

2.2 FFT转换模块

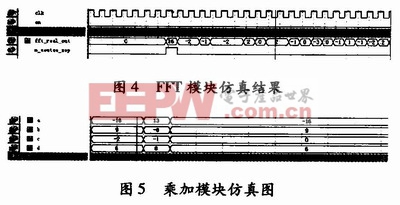

该模块是本设计的核心模块,由输入缓冲器、FFT运算器、控制器构成,完成对数据的FFT变换。将PN码发生器产生的数据存入输入缓冲器中,在控制器的控制下,FFT运算模块从输入缓冲器中读取出数据值进行FFT变换,然后得出输出数据。图3所示为FFT模块的输入输出关系。fft_imag_out,fft_real_out分别为输出数据的实部、虚部和修正因子,m_soutoe_sop为输出数据的起始位。

2.3 计算模块

设两路信号进行FFT后的数据为

可见对进行FFT变换后需要进行的运算处理其实质是一个乘加,一个乘减和一个加法运算,其中乘加运算仿真结果如图4、图5所示。

加入微信

获取电子行业最新资讯

搜索微信公众号:EEPW

或用微信扫描左侧二维码